# 16 MULTI-FUNCTION LED DRIVER AND GPIO CONTROLLER WITH I<sup>2</sup>C INTERFACE

#### **FEATURES**

- 16 multi-function I/O, each for LED drive (current-source dimming) or GPIO mode

- 256 steps linear dimming in LED drive mode

- Any GPIO can be configured as an input or an output independently

- Support interrupt, 8µs deglitch, low-level active

- Standard I<sup>2</sup>C interface, AD1/AD0 select I<sup>2</sup>C device address

- SDA, SCL, RSTN, and all GPIO can accept in 1.8V logic input

- Supply shutdown function, low-level active

- 2.5V~5.5V power supply

#### **APPLICATIONS**

Cell Phone

PDA/MP3/MP4/CD/Mini display

#### **GENERAL DESCRIPTION**

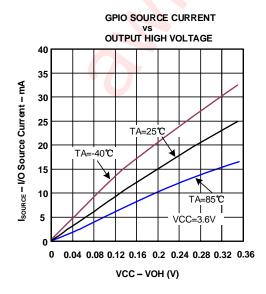

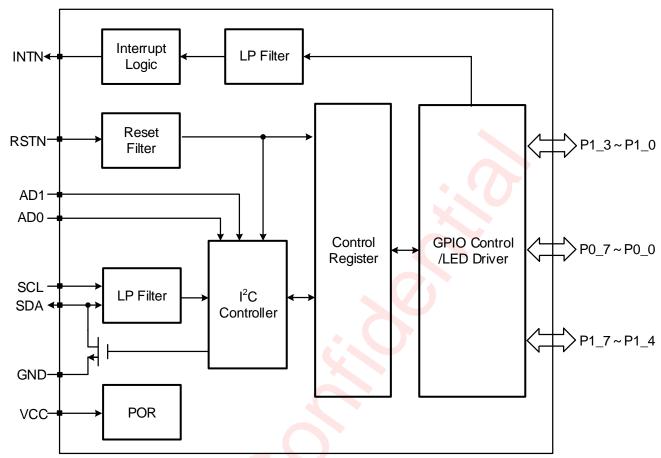

AW9523B is a 16 multi-function LED driver and GPIO controller. Any of the 16 I/O ports can be configured as LED drive mode or GPIO mode. Furthermore, any GPIO can be configured as an input or an output independently.

After power on, all the 16 I/O ports are configured as GPIO output as default, which default states are set according to the I<sup>2</sup>C device address selection inputs, AD0 and AD1. All I/O ports configured as inputs are continuously monitored for state changes. State changes are indicated by the INTN output. When AW9523B reads GPIO state through the I<sup>2</sup>C interface, the interrupt is cleared. Interrupt has 8µs deglitch.

When the I/O ports are configured as LED drive mode, AW9523B can set the current of LED drive between 0~IMAX by I<sup>2</sup>C interface, which is divided by 256 steps linear dimming. The default maximum current (IMAX) is 37mA, and IMAX can be changed in GCR register.

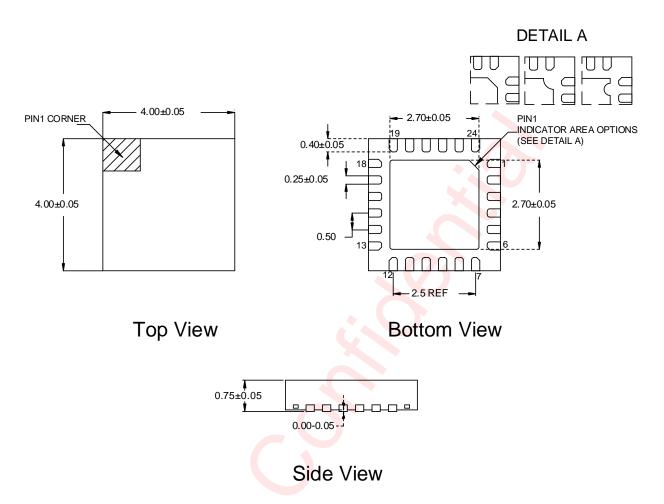

AW9523B is available in QFN4mm×4mm×0.75mm -24L package, and 2.5V~5.5V power supply.

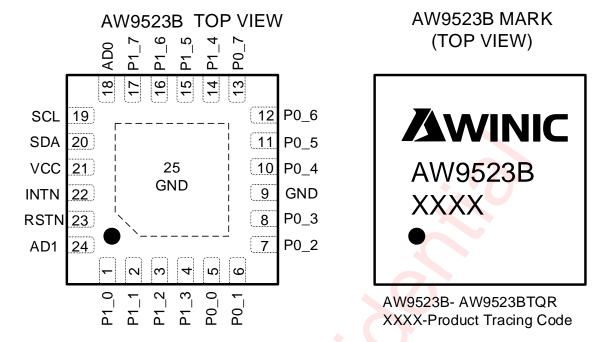

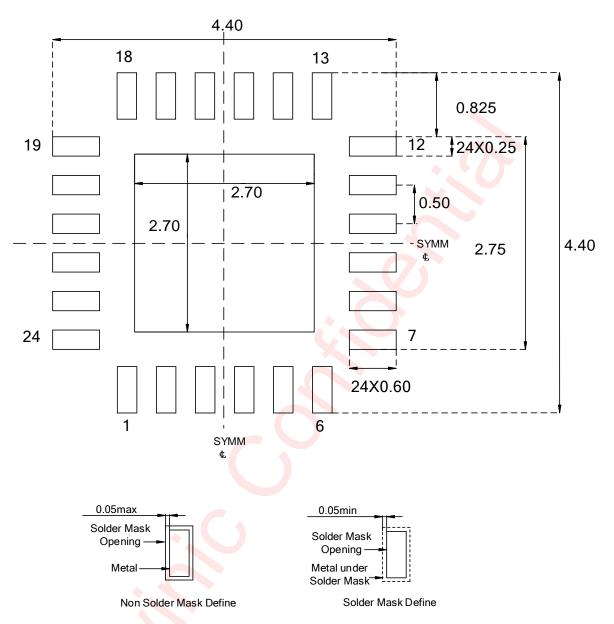

#### PIN CONFIGURATION AND MARKING

Figure 1 AW9523B PIN CONFIGURATION AND MARKING

All trademarks are the property of their respective owners.

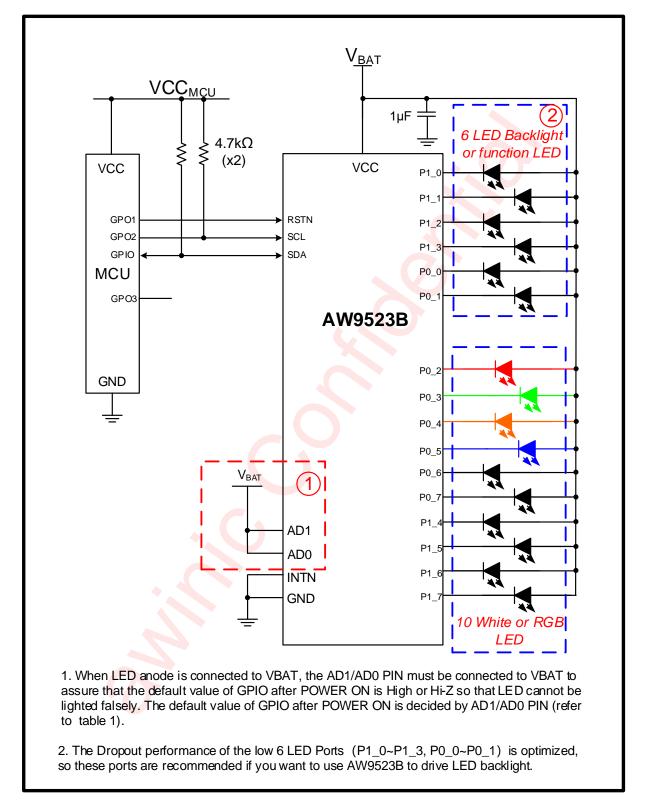

#### TYPICAL APPLICATION CIRCUITS

Figure 2 Drive 16 function LED, including 6 ports feasible for LED backlight

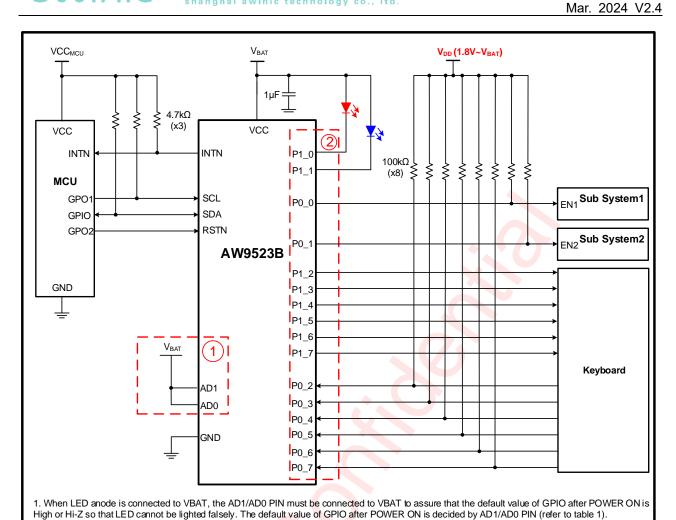

2. Any of the 16 I/O ports can be configured as LED drive mode or GPIO mode. In the application schematic, P1\_0, P1\_1 are configured as LED mode, P0\_0, P0\_1 is configured as GPIO output to control sub system, P1\_2~P1\_7 are configured as GPIO output to drive the row line of keyboard, P0\_2~P0\_7 are configured as GPIO input to drive the column line of keyboard.

### **PIN DEFINITION**

| Pin No. | Name | Description                                                                                                                                                                  |

|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | P1_0 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 2       | P1_1 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 3       | P1_2 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 4       | P1_3 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 5       | P0_0 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 6       | P0_1 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 7       | P0_2 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 8       | P0_3 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 9       | GND  | Ground supply                                                                                                                                                                |

| 10      | P0_4 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 11      | P0_5 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 12      | P0_6 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 13      | P0_7 | GPIO mode default, input or output, open-drain (default) or push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN. |

| 14      | P1_4 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 15      | P1_5 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 16      | P1_6 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 17      | P1_7 | GPIO mode default, input or output, push-pull mode. Can be configured as LED drive mode. The default state after power on is related to AD1/AD0 PIN.                         |

| 18      | AD0  | I <sup>2</sup> C interface device address, connect to VBAT or GND, and control the default state of output pin (refer to table 1).                                           |

| 19      | SCL  | I <sup>2</sup> C interface clock bus                                                                                                                                         |

| 20      | SDA  | I <sup>2</sup> C interface data bus                                                                                                                                          |

| 21      | VCC  | Power supply                                                                                                                                                                 |

| 22      | INTN | Interrupt output pin, open-drain mode, need external pull-up resistor; interrupt low active.                                                                                 |

| 23      | RSTN | Hardware reset pin, low reset; it has an internal 100 kΩ(typical) pull-low resistor.                                                                                         |

| 24      | AD1  | I <sup>2</sup> C interface device address, connect to VBAT or GND, and control the default state of output pin (refer to table 1).                                           |

| 25      | GND  | Ground supply                                                                                                                                                                |

|         | 1    | <u> </u>                                                                                                                                                                     |

#### ORDERING INFORMATION

| Part Number | Temperature  | Package            | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-------------|--------------|--------------------|---------|----------------------------------|------------------------------|---------------------------------|

| AW9523BTQR  | -40°C ~ 85°C | 4mm×4mm<br>QFN-24L | AW9523B | MSL3                             | RoHS+HF                      | 6000 units/<br>Tape and<br>Reel |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARAMETERS                                                    | RANGE          |  |  |

|---------------------------------------------------------------|----------------|--|--|

| Supply voltage, VCC                                           | -0.3V to 6 V   |  |  |

| SCL, SDA, AD0, AD1, INTN, RSTN, P0_0~P0_7,<br>P1_0~P1_7       | -0.3V to 6V    |  |  |

| Max power (P <sub>Dmax</sub> , package@ T <sub>A</sub> =25°C) | 3.2 W          |  |  |

| Package thermal impedance, θ <sub>JA</sub>                    | 31°C/W         |  |  |

| Max junction temperature, T <sub>Jmax</sub>                   | 150°C          |  |  |

| Storage Temperature T <sub>STG</sub>                          | -65°C to 150°C |  |  |

| Lead Temperature (Soldering 10 Seconds)                       | 260°C          |  |  |

| ESD <sup>(NOTE 2)</sup>                                       |                |  |  |

| НВМ                                                           | ±2000V         |  |  |

| CDM                                                           | ±1500V         |  |  |

| Latch-Up                                                      |                |  |  |

| Test Condition:                                               | +IT: 200mA     |  |  |

| JEDEC STANDARD NO.78E NOVEMBER 2016                           | -IT: -200mA    |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: MIL-STD-883J Method 3015.9. JEDEC EIA/JESD22-C101F(CDM).

# **Recommended Operating Conditions**

| Symbol          | Parameter                            | Min. | Тур. | Max. | Unit     |

|-----------------|--------------------------------------|------|------|------|----------|

| VCC             | Input voltage                        | 2.5  | 3.6  | 5.5  | <b>\</b> |

| C <sub>IN</sub> | Input capacitance                    | 0.1  | 1    | 100  | μF       |

| T <sub>A</sub>  | Operating free-air temperature range | -40  | 25   | 85   | °C       |

# **ELECTRICAL CHARACTERISTICS**

V<sub>CC</sub>=3.8V, T<sub>A</sub>=25°C for typical values (unless otherwise noted)

|                       | Parameter                                                                 | Test Con                                         | Min.                   | Тур.        | Max. | Unit |    |

|-----------------------|---------------------------------------------------------------------------|--------------------------------------------------|------------------------|-------------|------|------|----|

| Supply vo             | Itage and current                                                         | l                                                |                        |             |      |      | I. |

| VCC                   | Supply voltage                                                            |                                                  |                        | 2.5         |      | 5.5  | V  |

| I <sub>shutdown</sub> | Shutdown current                                                          | RSTN=0                                           | GND                    |             | 0.1  | 5    | μA |

|                       |                                                                           | RSTN=1.8V;<br>$V_1 = GND \text{ or}$             | VCC=5.5V               |             | 30   | 60   | μΑ |

| I <sub>cc</sub>       |                                                                           | VCC;<br>AD0=AD1=GND;                             | VCC=3.6V               |             | 10   | 20   | μA |

|                       | Standby mode                                                              | I <sub>O</sub> =0mA;<br>F <sub>SCL</sub> =0kHz   | VCC=2.7V               |             | 2    | 5    | μA |

|                       | Standay mede                                                              | RSTN=1.8V<br>$V_1 = GND \text{ or}$              | VCC=5.5V               |             | 50   | 80   | μA |

|                       |                                                                           | VCC;<br>AD0=AD1=GND;                             | VCC=3.6V               |             | 12   | 24   | μA |

|                       |                                                                           | I <sub>O</sub> =0mA;<br>F <sub>SCL</sub> =400kHz | VCC=2.7V               |             | 6    | 10   | μA |

| LED Drive             | r                                                                         |                                                  |                        |             |      |      |    |

| $I_{MAX}$             | Max current of LED drive                                                  | Configure DIMx                                   | Reg. as FFH            | 31.9        | 37   | 43.1 | mA |

| $V_{drop1}$           | Dropout voltage on low<br>6 ports (P1-0~P1_3,<br>P0_0~P0_1)               | I <sub>оит</sub> =20                             | lmA                    |             | 60   |      | mV |

| $V_{\text{drop2}}$    | Dropout voltage on high<br>10 ports (P0-2~P0_7,<br>P1_4~P1_7)             | I <sub>оит</sub> =20                             |                        | 80          |      | mV   |    |

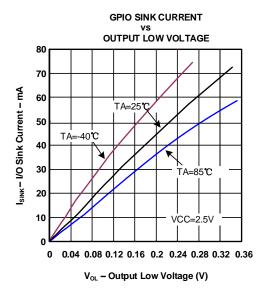

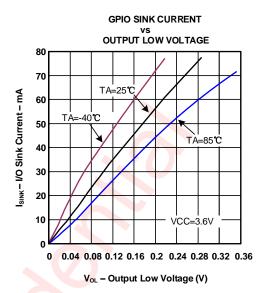

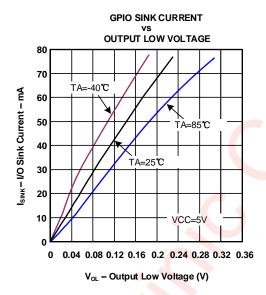

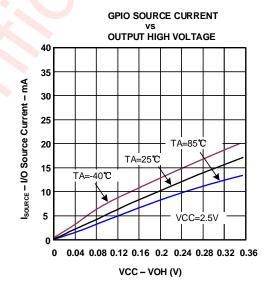

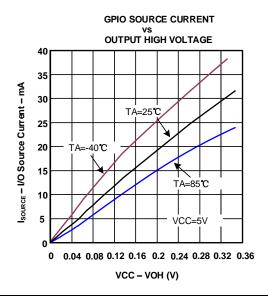

| Digital pin           | output                                                                    |                                                  |                        |             |      |      |    |

|                       |                                                                           | VCC=2.5V, I <sub>SC</sub>                        |                        | VCC-<br>170 |      | mV   |    |

| $V_{OH}$              | High-level output voltage (P0_7~P0_0, P1_7~P1_0)                          | VCC=3.6V, I <sub>SC</sub>                        |                        | VCC-<br>250 |      | mV   |    |

|                       |                                                                           | VCC=5V, I <sub>SOL</sub>                         |                        | VCC-<br>200 |      | mV   |    |

|                       | Low-level output voltage                                                  | VCC=2.5V, I                                      | <sub>SINK</sub> =20mA  |             | 90   |      | mV |

| $V_{\text{OL}}$       | (P0_7~P0_0,                                                               | VCC=3.6V,I <sub>3</sub>                          | SINK=20mA              |             | 70   |      | mV |

|                       | P1_7~P1_0)                                                                | VCC=5V, I <sub>SI</sub>                          |                        | 60          |      | mV   |    |

|                       |                                                                           | VCC=2.5V,                                        | I <sub>SINK</sub> =6mA |             | 150  |      | mV |

| $V_{OL}$              | Low-level output voltage (SDA, INTN)                                      | VCC=3.6V,                                        | I <sub>SINK</sub> =6mA |             | 100  |      | mV |

|                       | (CD) (G HVIIV)                                                            | VCC=5V, I <sub>S</sub>                           | <sub>SINK</sub> =6mA   |             | 75   |      | mV |

| Digital pin           | input                                                                     | •                                                |                        |             |      |      | ·  |

| V <sub>IH</sub>       | High-level input voltage (SCL, SDA, RSTN, AD0, AD1, P0_7~P0_0, P1_7~P1_0) |                                                  |                        | 1.4         |      |      | V  |

| V <sub>IL</sub>       | Low-level input voltage (SCL, SDA, RSTN, AD0, AD1, P0_7~P0_0, P1_7~P1_0)  |                                                  |                        |             |      | 0.4  | V  |

Mar. 2024 V2.4

| I <sub>IH</sub> , I <sub>IL</sub> | Input current (SCL,<br>SDA, AD0, AD1,<br>P0_7~P0_0,<br>P1_7~P1_0)  | V <sub>I</sub> =VCC or GND | -0.2 |      | +0.2 | μА |

|-----------------------------------|--------------------------------------------------------------------|----------------------------|------|------|------|----|

| R_ <sub>RSTN</sub>                | internal pull-low resistor<br>in RSTN PIN                          |                            |      | 100k |      | Ω  |

| Cı                                | Input capacitance (SCL, SDA, RSTN, AD0, AD1, P0_7~P0_0, P1_7~P1_0) | V <sub>I</sub> =VCC or GND |      | 3    |      | pF |

| t <sub>SP_RSTN</sub>              | Pulse width that RSTN<br>PIN can filter                            | RSTN=VCC                   |      | 10   |      | μs |

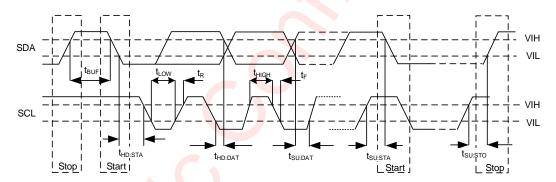

# **12C INTERFACE TIMING REQUIREMENTS**

| Parameter                                                         | Symbol              | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------------------|---------------------|------|------|------|------|

| SCL I <sup>2</sup> C clock frequency                              | f <sub>SCL</sub>    |      |      | 400  | kHz  |

| I <sup>2</sup> C Start or repeated Start condition hold time      | thd:STA             | 0.6  |      |      | μs   |

| SCL I <sup>2</sup> C clock low time                               | t <sub>LOW</sub>    | 1.3  |      |      | μs   |

| SCL I <sup>2</sup> C clock high time                              | thigh               | 0.6  |      |      | μs   |

| I <sup>2</sup> C Start or repeated Start condition setup time     | tsu:sta             | 0.6  |      |      | μs   |

| I <sup>2</sup> C serial-data hold time                            | t <sub>HD:DAT</sub> | 0    |      |      | μs   |

| I <sup>2</sup> C serial-data setup time                           | t <sub>SU:DAT</sub> | 0.1  |      |      | μs   |

| I <sup>2</sup> C rise time                                        | t <sub>R</sub>      |      |      | 0.3  | μs   |

| I <sup>2</sup> C fall time                                        | t <sub>F</sub>      |      |      | 0.3  | μs   |

| I <sup>2</sup> C Stop condition setup time                        | tsu:sто             | 0.6  |      |      | μs   |

| I <sup>2</sup> C bus free time between a STOP and START condition | t <sub>BUF</sub>    | 1.3  |      |      | μs   |

| I <sup>2</sup> C spike time                                       | tsp                 | 0    |      | 50   | ns   |

| I <sup>2</sup> C bus capacitive load                              | Cb                  |      |      | 400  | pF   |

Figure 4 I<sup>2</sup>C Interface Timing

#### **TYPICAL CHARACTERISTICS**

Ambient temperature is 25°C, input voltage is 3.6 V, unless otherwise noted .

#### **FUNCTIONAL BLOCK**

Figure 5 AW9523B Functional Block

#### **DETAILED DESCRIPTION**

AW9523B is a 16 multi-function IO controller, which is applied for LED drive or GPIO. Any of the 16 I/O ports can be configured as LED drive mode or GPIO mode. Furthermore, any GPIO can be configured as an input or an output independently.

When configured as GPIO mode, all I/O ports configured as inputs are continuously monitored for state changes. State changes are indicated by the INTN output. When AW9523B read GPIO state through the I<sup>2</sup>C interface, the interrupt is cleared.

When configured as LED drive, drive current range is 0~IMAX, which has 256 steps. Default IMAX is 37mA, and it can be changed in GCR register.

#### **POWER ON**

After power-up, about 100µs delay is required before RSTN set to high, otherwise, the device may work incorrectly. The minimal wait time for I<sup>2</sup>C communication is 5ms, during this period, some internal modules (such as LDO) start to work and reach a stable state.

Below is the recommended operation timing:

Figure 6 AW9523B Power On

#### **GPIO OUTPUT**

After power on, all the 16 I/O ports are configured as GPIO output as default, which default states are set according to the I<sup>2</sup>C slave address selection inputs, AD0 and AD1, refer to table 1 for detail. The P1 port is Push-Pull mode; P0 port is Open-Drain mode (default) and can be configured as Push-Pull mode. When P0 port is Open-Drain mode, it need pull-up resistor.

Table 1. Default state of IO ports , AD1/AD0 and P0\_x/P1\_x

| AD1  | AD0  | P1_7 | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P1_0 | P0_7 | P0_6 | P0_5 | P0_4 | P0_3 | P0_2 | P0_1 | P0_0 |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| GND  | GND  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| GND  | VBAT | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | Hi-Z | Hi-Z | Hi-Z | Hi-Z |

| VBAT | GND  | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | Hi-Z | Hi-Z | Hi-Z | Hi-Z | 0    | 0    | 0    | 0    |

| VBAT | VBAT | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | Hi-Z |

#### GPIO INPUT/OUTPUT DIRECTION SELECT

The register Config\_Port0 and Config\_Port1 can configure a port as input or output. Each bit of the register is corresponding to each port, the bit set '1' as input, '0' as output. The default value is '0' as output.

#### **GPIO INPUT**

User can get the current state of GPIO through reading the register Input\_Port0 and Input\_Port1 by I<sup>2</sup>C Interface. AW9523B GPIO support 1.8V logic input.

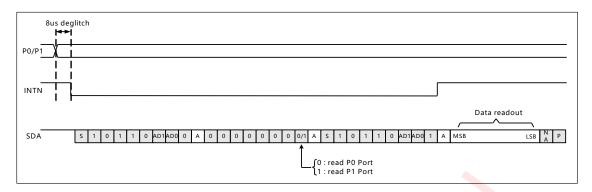

#### **INTERRUPT**

AW9523B can monitor IO state to generate interrupt when configure port as GPI and GPIO interrupt enabled. External MCU is required acknowledge by INTN pin. INTN is open-drain output, low-level active, and need external pull-up resistor.

When AW9523B detect port change, any input state from high-level to low-level or from low-level to high-level will generate interrupt after 8us internal deglitch. External MCU read Input\_Port0/1 register to clear interrupt.

Once interrupt is generated, all the Input\_Port0/1 registers must be read through I2C read operation separately to clear the interrupt.

Figure 7 Interrupt generation and clear

#### **LED DRIVE**

AW9523B is co-anode current source LED drive. LED drive IMAX is configured by GCR (ISEL) register, to select 4 grades. The default IMAX is 37mA.

In LED drive mode, LED dim step can be manually controlled by external MCU. Drive current is from 0~IMAX divided by 256 steps.

Table 2. 256 steps dimming

| DIMx bit |   |   |   |   |   |   |   |                          |

|----------|---|---|---|---|---|---|---|--------------------------|

| 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | D                        |

| 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | OFF                      |

| 0        | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1/255×I <sub>MAX</sub>   |

| 0        | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 2/255×I <sub>MAX</sub>   |

|          |   |   |   |   |   |   |   |                          |

| 1        | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 253/255×I <sub>MAX</sub> |

| 1        | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 254/255×I <sub>MAX</sub> |

| 1        | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 255/255×I <sub>MAX</sub> |

#### **12C INTERFACE**

AW9523B support I<sup>2</sup>C interface. The bidirectional I<sup>2</sup>C bus consists of the serial clock (SCL) and serial data (SDA) lines. Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

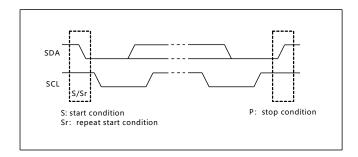

I<sup>2</sup>C communication with this device is initiated by a master sending a Start condition, a high-to-low transition on the SDA input/output while the SCL input is high. After the Start condition, the device address byte is sent, MSB first, including the data direction bit (R/W). This device does not respond to the general call address.

After receiving the valid address byte, this device responds with an ACK, a low on the SDA input/output during the high of the ACK-related clock pulse. The address inputs (AD1/AD0) of the slave device must not be changed between the Start and Stop conditions.

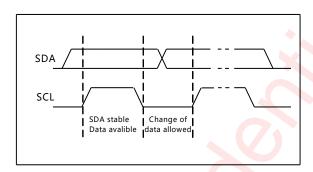

On the I<sup>2</sup>C bus, only one data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high pulse of the clock period, as changes in the data line at this time are interpreted as control commands (Start or Stop).

A Stop condition, a low-to-high transition on the SDA input/output while the SCL input is high, is sent by the master.

Figure 8 Start and stop condition

Figure 9 Bit Transfer

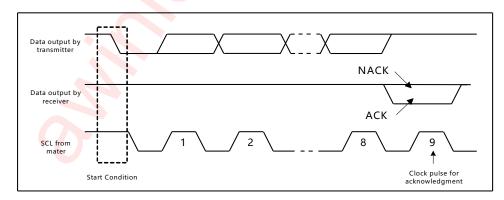

Any number of data bytes can be transferred from the transmitter to the receiver between the Start and the Stop conditions. Each byte of eight bits is followed by one ACK bit. The transmitter must release the SDA line before the receiver can send an ACK bit. The device that acknowledges must pull down the SDA line during the ACK clock pulse so that the SDA line is stable low during the high pulse of the ACK-related clock period. When a slave receiver is addressed, it must generate an ACK after each byte is received. Similarly, the master must generate an ACK after each byte that it receives from the slave transmitter. Setup and hold times must be met to ensure proper operation.

A master receiver signals an end of data to the slave transmitter by not generating an acknowledge (NACK) after the last byte has been clocked out of the slave. This is done by the master receiver by holding the SDA line high. In this event, the transmitter must release the data line to enable the master to generate a Stop condition.

Figure 10 Acknowledgment On I<sup>2</sup>C Bus

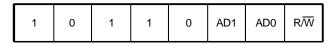

#### **DEVICE ADDRESS**

Below is the device address of AW9523B. AD1/AD0 bit in device address match with AD1/AD0 pin respectively.

AD1/AD0 value match with AW9523B pin AD1/AD0 respectively

Figure 11 AW9523B Device Address

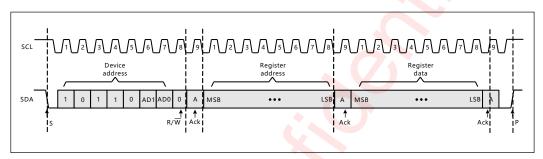

#### **WRITE**

Data is transmitted to the AW9523B by sending the device address and setting the least-significant bit to a logic 0. The register address byte is sent after the device address and determines which register receives the data that follows the command byte.

After sending data to one register, the next data byte is sent to the other register. There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

Figure 12 AW9523B Write Operation

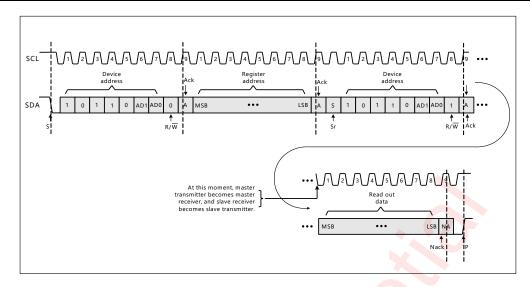

#### **READ**

The bus master first must send the AW9523B address with the least-significant bit set to a logic 0. The register address byte is sent after the address and determines which register is accessed. After a restart, the device address is sent again, but this time, the least-significant bit is set to a logic 1. Data from the register defined by the register address byte then is sent by the AW9523B.

After a restart, the value of the register defined by the register address byte matches the register being accessed when the restart occurred. Data is clocked into the register on the rising edge of the ACK clock pulse. After the first byte is read, additional bytes may be read, but the data now reflect the information in the other register.

Data is clocked into the register on the rising edge of the ACK clock pulse. There is no limitation on the number of data bytes received in one read transmission, but when the final byte is received, the bus master must not acknowledge the data.

Figure 13 AW9523B Read Operation

#### **RESET FUNCTION**

AW9523B support 3 reset mode: power on reset, hardware reset, software reset. Each reset mode can reset registers to default value.

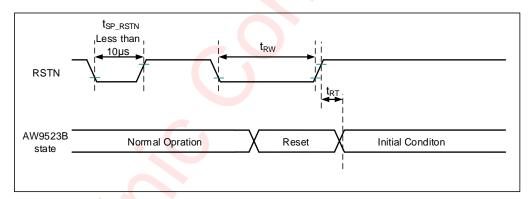

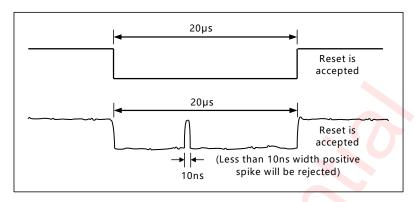

#### HARDWARE RESET

Hardware reset timing is as the following figure.

Figure 14 Hardware Reset Timing

Table 3. Hardware Reset Parameter

|                 | Parameter                   | Condition              | min | typ | max | unit |

|-----------------|-----------------------------|------------------------|-----|-----|-----|------|

| t <sub>RW</sub> | Reset pulse low level width | VSS=0V, VCC=2.4V~5.5V, | 20  |     |     | μs   |

| t <sub>RT</sub> | Reset recovery time         | T=-40℃~125℃            | 1   |     |     | μs   |

#### Note:

1. The hardware reset PIN (RSTN) has a built-in deglitch block. Spike due to an electrostatic discharge on RSTN line does not cause irregular system reset according to the table below:

| Reset pulse (RSTN)          | AW9523B action |

|-----------------------------|----------------|

| Shorter than 10µs (typical) | Reset Rejected |

| Longer than 20µs            | Reset          |

- 2. After reset, AW9523B is in default state. All GPIO are configured as output, which value is decided by 2 device address (AD1/AD0) (refer to table 1). The interrupt (INTN) is cleared and pulled up by external pull-up resistor.

- 3. Spike Rejection also applies during a valid reset pulse as shown below:

Figure 15 Operation When RSTN SLOW

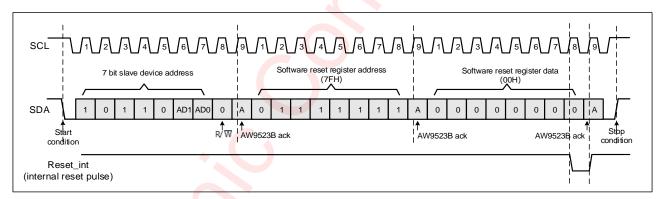

#### SOFTWARE RESET

AW9523B support software reset mode. Writing 00H to the software register(7FH) will generate a reset pulse. After software reset, AW9523B is in default state, which is the same as hardware reset. The software reset timing is as below. After the software reset command is send through the I<sup>2</sup>C interface, it takes at least 1ms for chip to acknowledge the new I<sup>2</sup>C command.

Figure 16 Software Reset Timing

# **REGISTERS**

Table 4. AW9523B register list

| Address | W/R | Default Value    | Function        | Description                 |

|---------|-----|------------------|-----------------|-----------------------------|

| 00H     | R   | Equal to P0      | Input_Port0     | P0 port input state         |

| 01H     | R   | Equal to P1      | Input_Port1     | P1 port input state         |

| 02H     | W/R | Refer to table 1 | Output_Port0    | P0 port output state        |

| 03H     | W/R | Refer to table 1 | Output_Port1    | P1 port output state        |

| 04H     | W/R | 00H              | Config_Port0    | P0 port direction configure |

| 05H     | W/R | 00H              | Config_Port1    | P1 port direction configure |

| 06H     | W/R | 00H              | Int_Port0       | P0 port interrupt enable    |

| 07H     | W/R | 00H              | Int_Port1       | P1 port interrupt enable    |

| 10H     | R   | 23H              | ID              | ID register (read only)     |

| 11H     | W/R | 00H              | CTL             | Global control register     |

| 12H     | W/R | FFH              | LED Mode Switch | P0 port mode configure      |

| 13H     | W/R | FFH              | LED Mode Switch | P1 port mode configure      |

| 20H     | W   | 00H              | DIM0            | P1_0 LED current control    |

| 21H     | W   | 00H              | DIM1            | P1_1 LED current control    |

| 22H     | W   | 00H              | DIM2            | P1_2 LED current control    |

| 23H     | W   | 00H              | DIM3            | P1_3 LED current control    |

| 24H     | W   | 00H              | DIM4            | P0_0 LED current control    |

| 25H     | W   | 00H              | DIM5            | P0_1 LED current control    |

| 26H     | W   | 00H              | DIM6            | P0_2 LED current control    |

| 27H     | W   | 00H              | DIM7            | P0_3 LED current control    |

| 28H     | W   | 00H              | DIM8            | P0_4 LED current control    |

| 29H     | W   | 00H              | DIM9            | P0_5 LED current control    |

| 2AH     | W   | 00H              | DIM10           | P0_6 LED current control    |

| 2BH     | W   | 00H              | DIM11           | P0_7 LED current control    |

| 2CH     | W   | 00H              | DIM12           | P1_4 LED current control    |

| 2DH     | W   | 00H              | DIM13           | P1_5 LED current control    |

| 2EH     | W   | 00H              | DIM14           | P1_6 LED current control    |

| 2FH     | W   | 00H              | DIM15           | P1_7 LED current control    |

| 7FH     | W   | 00H              | SW_RSTN         | Soft reset                  |

| Other   | -   | -                | -               | Reserved                    |

#### REGISTER DETAIL DESCRIPTION

Table 5. Input state register (00H, 01H)

| Address | Name        | Description                                            | Default |

|---------|-------------|--------------------------------------------------------|---------|

| 00H     | Input_Port0 | P0 port current logic state, 0-low level; 1-high level | Χ       |

| 01H     | Input_Port1 | P1 port current logic state, 0-low level; 1-high level | Х       |

The Input state registers (00H,01H) reflect the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by the Configuration Register. It only acts on read operation. Writes to these registers have no effect. The default value, X, is determined by the externally applied logic level.

Before a read operation, a write transmission is sent with the command byte to let the I<sup>2</sup>C device know that the Input Port registers will be accessed next.

Table 6. Output state register (02H, 03H)

| Address | Name         | Description                                         | Default         |

|---------|--------------|-----------------------------------------------------|-----------------|

| 02H     | Output_Port0 | Set P0 port output value. 0-low level; 1-high level | Refer to table1 |

| 03H     | Output_Port1 | Set P1 port output value. 0-low level; 1-high level | Refer to table1 |

The Output state register (02H, 03H) show the outgoing logic levels of the pins defined as outputs by the Configuration register. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 7. Configuration register (04H, 05H)

| Address | Name         | Description                                         | Default |

|---------|--------------|-----------------------------------------------------|---------|

| 04H     | Config_Port0 | P0 port input/output mode select. 0-output; 1-input | 00H     |

| 05H     | Config_Port1 | P1 port input/output mode select. 0-output; 1-input | 00H     |

The Configuration registers (04H, 05H) configure the directions of the I/O pins. If a bit in this register is set to 1, the corresponding port pin is enabled as an input with a high-impedance output driver. If a bit in this register is cleared to 0, the corresponding port pin is enabled as an output.

Table 8. Interrupt enable register (06H, 07H)

| Address | Name      | Description                                   | Default |

|---------|-----------|-----------------------------------------------|---------|

| 06H     | Int_Port0 | P0 port interrupt enable. 0-enable; 1-disable | 00H     |

| 07H     | Int_Port1 | P1 port interrupt enable. 0-enable; 1-disable | 00H     |

The Interrupt enable register (06H, 07H) are used to configure the interrupt enable or disable of GPIO. If a bit in this register is set to 1, the interrupt function of the corresponding port pin is disabled. If a bit in this register is cleared to 0, the interrupt function of corresponding port pin is enabled.

Table 9. ID register (10H)

| Address | Name | Description                                      | Default |

|---------|------|--------------------------------------------------|---------|

| 10H     | ID   | ID register, read only, the readout value is 23H | 23H     |

ID register (10H) is a read only register which stores the device ID. The ID read value of AW9523B is 23H.

Table 10. GCR ,Global control register (11H)

| Address | Name     | Description                                                                                                     | Default |

|---------|----------|-----------------------------------------------------------------------------------------------------------------|---------|

| D[7:5]  | reserved | -                                                                                                               | -       |

| D[4]    | GPOMD    | Set P0 port GPIO output drive mode of D[4]=0, P0 port is Open-Drain mode; if D[4]=1, P0 port is Push-Pull mode. | 0       |

Mar. 2024 V2.4

| D[3:2] | reserved | -                                 | -  |

|--------|----------|-----------------------------------|----|

| D[1:0] | ISEL     | 256 step dimming range select     | 00 |

|        |          | 00: 0~I <sub>MAX</sub>            |    |

|        |          | 01: $0 \sim (I_{MAX} \times 3/4)$ |    |

|        |          | 10: $0 \sim (I_{MAX} \times 2/4)$ |    |

|        |          | 11: 0~(I <sub>MAX</sub> ×1/4)     |    |

D[4] is used to configure P0 port output drive as Open-Drain or Push-Pull mode. When P0 port use as output with Open-Drain mode, it needs pull-up resistor. If in Push-pull mode, it needs no pull-up resistor.

D[1:0] is used to configure the max drive current of LED. AW9523B set max current I<sub>MAX</sub> to 37mA(typical) default, and through register ISEL[1:0] can set to IMAX × 1/4, IMAX × 2/4, IMAX × 3/4, IMAX, so the 256 step dimming range changes.

Except D4, D[1:0], other bits (D[7:5]\D[3:2]) are used for test purpose and the default value is 0. If user needs to configure register 11H, then the bits D[7:5]\D[3:2] must configure to 0, or system function error may occur.

Table 11. LED mode switch register (12H)

| Address | Name            | Description                              | Default |

|---------|-----------------|------------------------------------------|---------|

|         |                 | Configure P0_7~P0_0 as LED or GPIO mode。 |         |

| 12H     | LED Mode Switch | 1: GPIO mode                             | FFH     |

|         |                 | 0: LED mode                              | ļ       |

LED mode switch register (12H) can configure P0 port as LED or GPIO mode. After reset, it is GPIO mode as default. Set a bit of 12H[7:0] to 0 so the corresponding port is LED mode, and set to 1 so the corresponding port is GPIO mode.

Table 12. LED mode switch register (13H)

| Address | Name            | Description                                                       | Default |

|---------|-----------------|-------------------------------------------------------------------|---------|

| 13H     | LED Mode Switch | Configure P1_7~P1_0 as LED or GPIO mode。 1: GPIO mode 0: LED mode | FFH     |

LED mode switch register (13H) can configure P1 port as LED or GPIO mode. After reset, it is GPIO mode as default. Set a bit of 13H[7:0] to 0 so the corresponding port is LED mode, and set to 1 so the corresponding port is GPIO mode.

Table 13. 256 step dimming control register (20H~2FH)

| Address | Name  | Description                   | Default |

|---------|-------|-------------------------------|---------|

| 20H     | DIM0  | P1_0 port LED current control | 00H     |

| 21H     | DIM1  | P1_1 port LED current control | 00H     |

| 22H     | DIM2  | P1_2 port LED current control | 00H     |

| 23H     | DIM3  | P1_3 port LED current control | 00H     |

| 24H     | DIM4  | P0_0 port LED current control | 00H     |

| 25H     | DIM5  | P0_1 port LED current control | 00H     |

| 26H     | DIM6  | P0_2 port LED current control | 00H     |

| 27H     | DIM7  | P0_3 port LED current control | 00H     |

| 28H     | DIM8  | P0_4 port LED current control | 00H     |

| 29H     | DIM9  | P0_5 port LED current control | 00H     |

| 2AH     | DIM10 | P0_6 port LED current control | 00H     |

| 2BH     | DIM11 | P0_7 port LED current control | 00H     |

| 2CH     | DIM12 | P1_4 port LED current control | 00H     |

| 2DH     | DIM13 | P1_5 port LED current control | 00H     |

| 2EH     | DIM14 | P1_6 port LED current control | 00H     |

| 2FH     | DIM15 | P1_7 port LED current control | 00H     |

The dimming control register (20H~2FH) are used to configure P0 port and P1 port LED current. Each port supports 256 step dimming. For the detailed configuration, refer to table 2.

#### Table 13.Soft reset register (7FH)

| Address | Name           | Description                         | Default |

|---------|----------------|-------------------------------------|---------|

| 7FH     | Software Reset | Write 00H to generate a reset pulse | Χ       |

The soft reset register (7FH) support software reset function, which brings convenience to software engineer. Every time write 00H to this register, it generate a reset pulse. The software reset timing, please refer to figure 14.

Table 14. Reserve register

| Address | Name                                               | Description |

|---------|----------------------------------------------------|-------------|

| 08H~0FH | Reserve register, for test purpose or not defined. | X           |

| 14H~1FH |                                                    |             |

| 30H~7EH | <b>♦ • • 7 7</b>                                   |             |

| 80H~FFH |                                                    |             |

Reserve register (08H~10H, 14H~1FH, 30H~7EH, 80H~FFH) are for test purpose or not defined, user should not write these registers, or may cause function error.

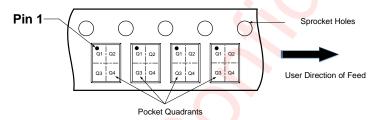

#### TAPE AND REEL INFORMATION

# REEL DIMENSIONS 0 D1 DO

# TAPE DIMENSIONS Cavity

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter D0: Reel Width

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### DIMENSIONS AND PIN1 ORIENTATION

| С  | 01  | D0   | A0   | В0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant  |

|----|-----|------|------|------|------|------|------|------|------|----------------|

| (m | nm) | (mm) | Filli Quaurant |

| 3  | 30  | 12.4 | 4.3  | 4.3  | 1.1  | 2    | 8    | 4    | 12   | Q1             |

All dimensions are nominal

#### **PACKAGE DESCRIPTION**

All Dimensions are in Millimeters

# **LAND PATTERN EXAMPLE**

All Dimensions are in Millimeter

# **REVISION HISTORY**

| Version | Date        | Change Record                                                                                                                                                                        |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0    | May 2014    | Officially Released                                                                                                                                                                  |

| V1.1    | August 2016 | Corrected Ordering Information part                                                                                                                                                  |

| V1.2    | July 2018   | <ol> <li>Updated Absolute Maximum Ratings part</li> <li>Updated Electrical Characteristics part</li> <li>Added Tape and Reel Information</li> <li>Added Land pattern part</li> </ol> |

| V1.3    | Feb 2019    | <ol> <li>"85°C" modified to "125°C" Page 7</li> <li>Update T<sub>Jmax</sub> to "150°C" Page 7</li> <li>"85°C" modified to "125°C" Page 15</li> </ol>                                 |

| V1.4    | May 2019    | Add "Recommended operation timing" Page 12                                                                                                                                           |

| V1.5    | July 2019   | Add voltage range of V <sub>DD</sub> Page 4                                                                                                                                          |

| V1.6    | April 2020  | Add Icc of standby mode                                                                                                                                                              |

| V1.7    | July 2020   | Corrected Ordering Information part                                                                                                                                                  |

| V1.8    | Feb 2022    | 1. Updata PIN SCL,SDA,AD0,AD1,INTN,RSTN,P0_0~P0_7,P1_0~P <mark>1</mark> _7 range to 6V Page 7                                                                                        |

| V1.9    | Feb 2022    | Corrected DETAILED DESCRIPTION of INTERRUPT                                                                                                                                          |

| V2.0    | Mar 2022    | 1. Modified the way of clear INTERRUPT                                                                                                                                               |

| V2.1    | July 2022   | Tape and Reel updated                                                                                                                                                                |

| V2.2    | Aug 2022    | Corrected Tape and Reel Information                                                                                                                                                  |

| V2.3    | Sep 2022    | 1. Corrected POD                                                                                                                                                                     |

| V2.4    | Mar 2024    | 1. Correct the Imax of LED driverP8 2. Delete REFLOWP25                                                                                                                              |

#### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.