#### Aug. 2024 V1.2

# **5V Synchronous Buck Converter**

#### **Features**

- Up to 95% Efficiency

- 2.5V to 5.5V Input Voltage Range

- Adjustable Output Voltage from 0.6 V to VIN

- Low RDS(ON) Switches 110 mΩ / 75 mΩ

- 1.5MHz Typical Switching Frequency

- 2A Maximum Output Current

- Low Dropout With 100% Duty Cycle

- Power Save Mode for Light Load Efficiency

- 35µA Operating Quiescent Current

- Power Good Output

- Over Current Protection

- Over Temperature Protection

- Internal Soft Startup

- Available in DFN 2X2-8L, SOT23-5L and SOT23-6L Package

# **Applications**

Mobile Phones

Set Top Box

Wireless Router

General Purpose POL Supply

Network Video Camera

#### **General Description**

The AW37420 is a synchronous step-down buck DC-DC converter with high efficiency and low power consumption. The device integrates switches capable of delivering an output current up to 2 A.

The device operates at typically 1.5 MHz frequency pulse width modulation (PWM) at moderate to heavy load currents. At light load, the device automatically converts to Power Save Mode (PSM) to maintain high efficiency over the entire load current range. In shutdown, the current consumption less than  $2~\mu A$ .

The AW37420 provides an adjustable output voltage via an external resistor divider. It has internal soft start circuit to limit the inrush current during startup. Other features like over current protection, over temperature protection and power good are built-in. The device is available in DFN 2X2-8L, SOT23-5L and SOT23-6L package.

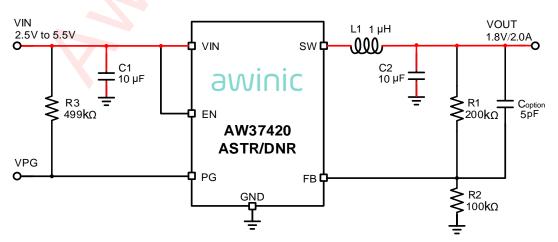

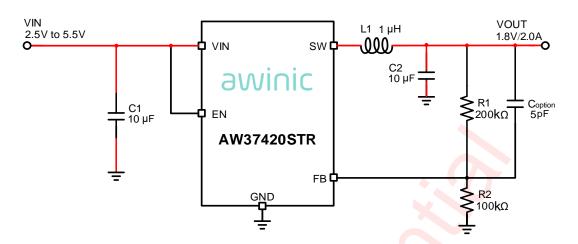

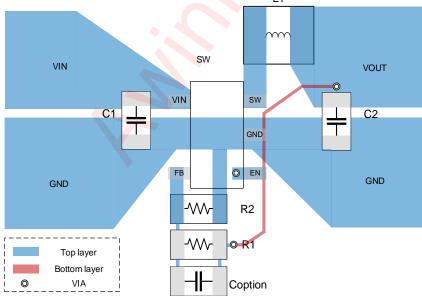

# **Typical Application Circuit**

1

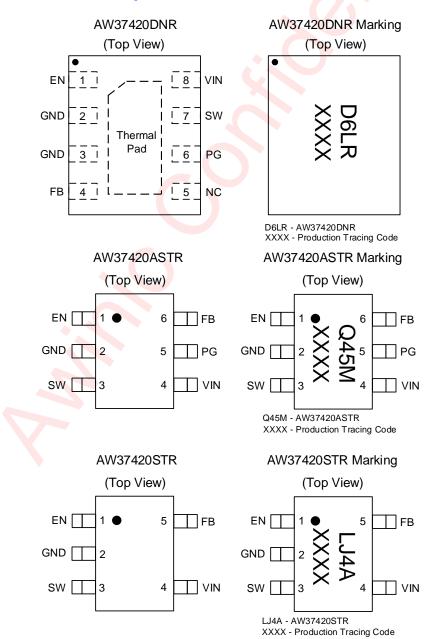

# **Pin Configuration And Top Mark**

# **Pin Definition**

|               | Pin No.      |              |      |                                                               |  |

|---------------|--------------|--------------|------|---------------------------------------------------------------|--|

| DFN<br>2×2-8L | SOT<br>23-6L | SOT<br>23-5L | NAME | DESCRIPTION                                                   |  |

| 1             | 1            | 1            | EN   | IC enable pin.                                                |  |

| 2             | 2            | 2            | GND  | Ground pin.                                                   |  |

| 3             | -            | -            | GND  | Ground pin.                                                   |  |

| 4             | 6            | 5            | FB   | Adjustable output voltage to converter's voltage feedback.    |  |

| 5             | -            | -            | NC   | Not connect                                                   |  |

| 6             | 5            | 1            | PG   | Power good open drain out pin.                                |  |

| 7             | 3            | 3            | SW   | Switch pin of the converter, it is connected to the inductor. |  |

| 8             | 4            | 4            | VIN  | IC power supply input.                                        |  |

Note: The thermal pad must be connected to GND.

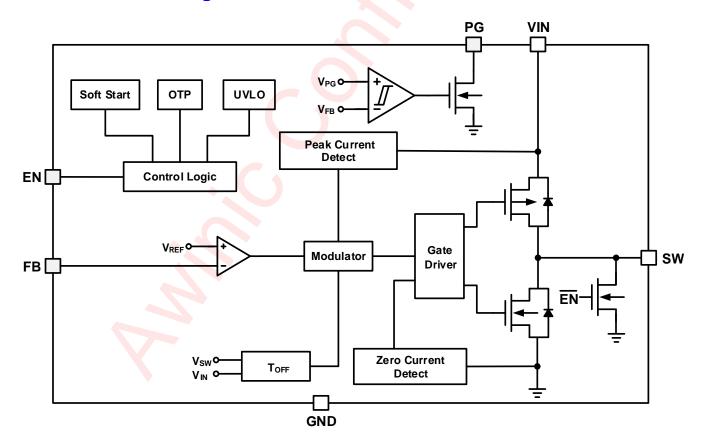

# **Functional Block Diagram**

# **Ordering Information**

| Part Number | Temperature  | Package    | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-------------|--------------|------------|---------|----------------------------------|------------------------------|---------------------------------|

| AW37420DNR  | -40°C ~ 85°C | DFN 2×2-8L | D6LR    | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and<br>Reel |

| AW37420ASTR | -40°C ~ 85°C | SOT23-6L   | Q45M    | MSL3                             | ROHS+HF                      | 3000 units/<br>Tape and<br>Reel |

| AW37420STR  | -40°C ~ 85°C | SOT23-5L   | LJ4A    | MSL3                             | ROHS+HF                      | 3000 units/<br>Tape and<br>Reel |

# **Absolute Maximum Ratings**(NOTE1)

| PARAM                  | PARAMETERS                                               |                        |  |  |  |  |

|------------------------|----------------------------------------------------------|------------------------|--|--|--|--|

|                        | VIN, EN, PG                                              | -0.3V to 6.5V          |  |  |  |  |

| Voltage                | SW(DC)                                                   | -0.3V to VIN+0.3V      |  |  |  |  |

| Voltage                | SW(AC, less than 10ns)                                   | -3V to 9V              |  |  |  |  |

|                        | FB                                                       | -0.3V to 5.5V          |  |  |  |  |

|                        |                                                          | 61.64°C/W (DFN 2×2-8L) |  |  |  |  |

| Junction-to-ambient th | Junction-to-ambient thermal resistance R <sub>BJA</sub>  |                        |  |  |  |  |

|                        |                                                          |                        |  |  |  |  |

| Maximum operating jun  | Maximum operating junction temperature T <sub>JMAX</sub> |                        |  |  |  |  |

| Storage temp           | erature T <sub>STG</sub>                                 | -65°C to 150°C         |  |  |  |  |

| Lead temperature (se   | oldering 10 seconds)                                     | 260°C                  |  |  |  |  |

|                        | ESD(Including CDM HBM                                    |                        |  |  |  |  |

| HBM <sup>(</sup>       | HBM <sup>(NOTE 2)</sup>                                  |                        |  |  |  |  |

| CDM(                   | ±1.5kV                                                   |                        |  |  |  |  |

|                        | Latch-Up                                                 |                        |  |  |  |  |

| Tost condition         | Test condition: JESD78E                                  |                        |  |  |  |  |

| rest conditio          | II. JEOD / OE                                            | -IT: -200mA            |  |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017.

NOTE3: All pins. Test Condition: ESDA/JEDEC JS-002-2018.

# **Recommended Operating Conditions**

| Symbol               | PARAMETERS                           | Min | Тур | Max | Unit |

|----------------------|--------------------------------------|-----|-----|-----|------|

| VIN                  | Input voltage                        | 2.5 |     | 5.5 | V    |

| VOUT                 | Output voltage                       | 0.6 |     | VIN | V    |

| IOUT                 | Output current                       | 0   |     | 2   | Α    |

| T <sub>A</sub>       | Operating free-air temperature range | -40 |     | 85  | °C   |

| I <sub>SINK_PG</sub> | Sink current at PG pin               |     |     | 1   | mA   |

# **Electrical Characteristics**

VIN=5.0V, T<sub>A</sub>=25°C for typical values (unless otherwise noted).

|                     | PARAMETER                           | TEST CONDITION                         | MIN      | TYP  | MAX   | UNIT |  |

|---------------------|-------------------------------------|----------------------------------------|----------|------|-------|------|--|

| SUPPLY              |                                     |                                        |          |      |       |      |  |

| IQ                  | Quiescent current into VIN pin      | Not switching                          |          | 35   |       | μΑ   |  |

| I <sub>SD</sub>     | Shutdown current into VIN pin       | EN =Low                                | <b>\</b> | 0.1  | 2     | μΑ   |  |

|                     | Under voltage lock out              | VIN falling                            |          | 2.37 | 2.45  | V    |  |

| Vuvlo               | Under voltage lock out hysteresis   |                                        |          | 130  |       | mV   |  |

| T <sub>OTP</sub>    | Over temperature pretection         | Junction temperature rising            |          | 150  |       | °C   |  |

| ГОТР                | Over temperature protection         | Junction temperature falling           |          | 120  |       | °C   |  |

| LOGIC IN            | TERFACE                             | , ,                                    |          |      |       |      |  |

| ViH                 | High-level threshold at EN pin      | 2.5 V ≤ VIN ≤ 5.5 V                    | 1.2      |      |       | V    |  |

| VIL                 | Low-level threshold at EN pin       | 2.5 V ≤ VIN ≤ 5.5 V                    |          |      | 0.4   | V    |  |

| tss                 | Soft startup time                   |                                        |          | 700  |       | μs   |  |

| $V_{PG}$            | Power good threshold                | VFB rising, referenced to VFB nominal  |          | 95   |       | %    |  |

| VPG                 | Power good threshold                | VFB falling, referenced to VFB nominal |          | 90   |       | %    |  |

| V <sub>PG,OL</sub>  | Power good low-level output voltage | I <sub>SINK</sub> = 1 mA               |          |      | 0.4   | V    |  |

| I <sub>PG,LKG</sub> | Input leakage current into PG pin   | V <sub>PG</sub> = 5.0 V                |          | 0.01 |       | μΑ   |  |

| t <sub>PG,DLY</sub> | Power good delay time               | VFB falling                            |          | 30   |       | μs   |  |

| OUTPUT              |                                     |                                        |          |      |       |      |  |

| V <sub>FB</sub>     | Feedback regulation voltage         |                                        | 0.588    | 0.6  | 0.612 | V    |  |

| D                   | High-side FET on resistance         |                                        |          | 110  |       | mO.  |  |

| R <sub>DS(on)</sub> | Low-side FET on resistance          |                                        |          | 75   |       | mΩ   |  |

| I <sub>LIM</sub>    | High-side FET current limit         |                                        |          | 3    |       | Α    |  |

| fsw                 | Switching frequency                 | VOUT = 2.5 V                           |          | 1.5  |       | MHz  |  |

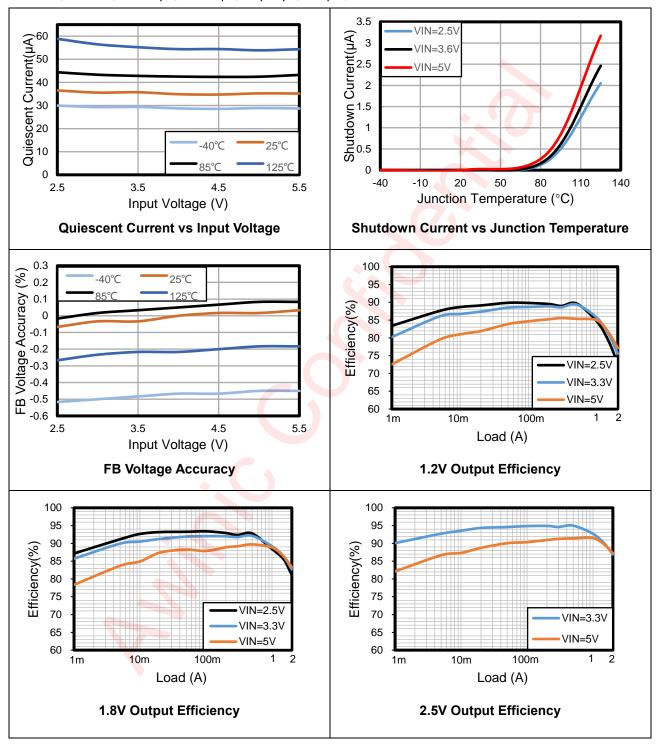

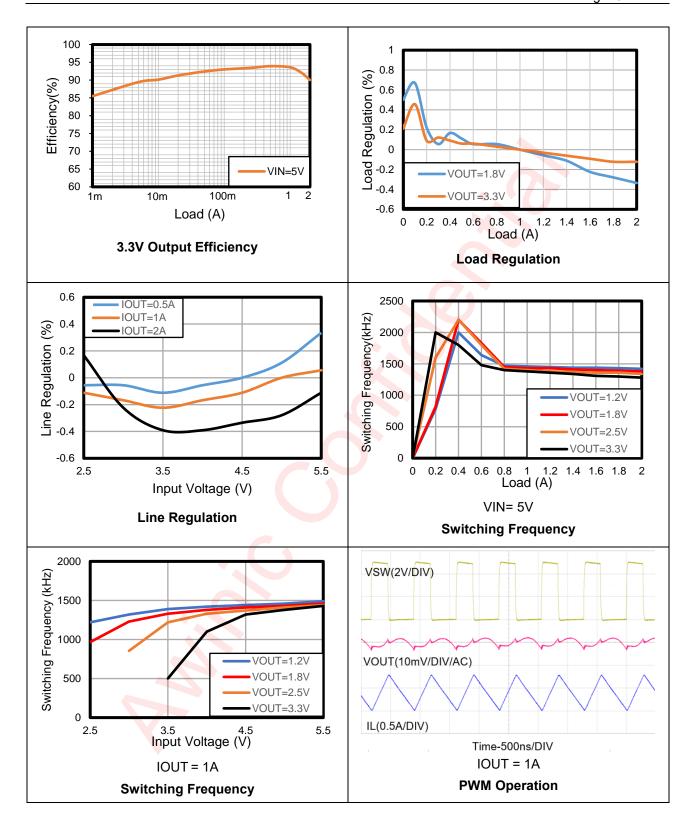

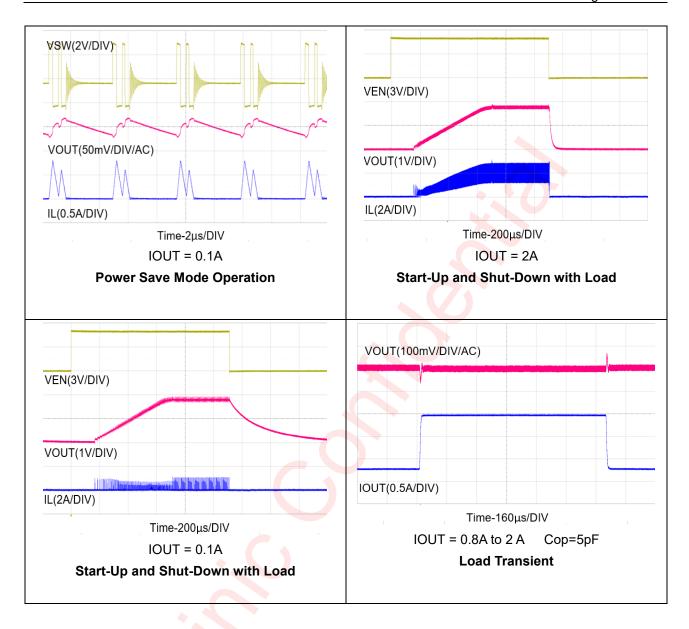

# **Typical Characteristics**

awinic

$T_A=25$ °C, VIN=5V, C1=10 $\mu$ F, C2=10 $\mu$ F, Cop=5pF, L=1 $\mu$ H, unless otherwise noted.

Aug. 2024 V1.2

### **Detailed Functional Description**

The AW37420 is a synchronous step-down buck DC-DC converter which operates with an adaptive off-time with peak current control scheme. At medium to heavy loads, the device operates in pulse width modulation (PWM) mode with 1.5MHz switching frequency. Based on the VIN/VOUT ratio, a circuit sets the required off time for the low-side MOSFET, which makes the switching frequency relatively constant regardless of the variation of input voltage, output voltage, and load current.

#### **Soft Reset**

Internal soft startup circuitry ramps up the output voltage after enabling the device. During a startup time, the AW37420 starts with the applied bias voltage and ramps the output voltage to its nominal value. This avoids excessive inrush current and creates a smooth output voltage rise slope. It also prevents excessive voltage drops of primary cells and rechargeable batteries with high internal impedance.

#### **Under-voltage Lockout**

An insufficient supply voltage may cause malfunctions in the device circuitry. An under-voltage lockout (UVLO) is implemented to avoid wrong operation of the device at low input voltages. It shuts down the device when voltages lower than  $V_{UVLO}$  with a hysteresis. When the input voltage exceeds the rising UVLO threshold, the device restarts with a fresh startup sequence. The hysteresis of UVLO is 120mV.

#### Switch Current Limit and Short Circuit Protection (HICCUP)

The AW37420 has the switch current limit, which can prevent the device from high inductor current and from drawing excessive current from the battery or input voltage rail. Excessive current might occur with a shorted or saturated inductor or an over load or shorted output circuit condition. When the inductor current reaches the threshold I<sub>LIM</sub>, the high-side MOSFET is turned off and the low-side MOSFET is turned on to ramp down the inductor current with an adaptive off-time.

When this switch current limits is triggered 32 times, the device reduces the current limit for further 32 cycles and then stops switching to protect the output. The device will start a new startup after a typical delay time of 500µs. The device repeats this mode until the high load condition disappears. HICCUP protection is also enabled during the startup.

#### Over temperature protection

To protect the device from overheating damage, the temperature of die is monitored. If it exceeds the shutdown threshold, the switching will be stopped and the device shuts down. Once the device temperature falls below the falling threshold, the device returns to normal operation automatically.

#### **Enable and Disable**

The AW37420 is enabled by setting the EN pin to logic high, and shutdown mode is forced when the EN pin is pulled low with a shutdown current of typically 0.1µA. In shutdown mode, the internal power switches as well as the entire control circuitry are turned off. An internal output discharge FET discharges the output through the SW pin smoothly.

Aug. 2024 V1.2

#### **Power Good**

The AW37420DNR and AW37420ASTR have a power good output. When the output is up to 95% of the nominal voltage, the PG pin goes high. The PG pin will be driven low when the output voltage falls to 90% of the nominal voltage.

The PG pin is an open-drain output, which specified to sink up to 1 mA. It requires a pull-up resistor connecting to any voltage rail less than 5.5V. The PG signal can be used to sequence multiple rails by connecting it to the EN pin of other converters. Leave the PG pin unconnected when not sed.

# Application Information

#### **Setting The Output Voltage**

The output voltage is set by an external resistor divider according to:

$$VOUT = V_{FB} \times \left(1 + \frac{R_1}{R_2}\right) = 0.6V \times \left(1 + \frac{R_1}{R_2}\right)$$

R<sub>2</sub> must not be higher than 100kΩ to achieve high efficiency at light load while providing acceptable noise sensitivity.

#### **Inductor Selection**

The main parameter for the inductor selection is the inductor value and then the saturation current of the inductor. The inductor current ripple is determined by the Inductance value. The below equation indicates how to calculate the maximum inductor current under static load conditions.

$$I_{L,MAX} = I_{LOAD,MAX} + \frac{\Delta I_L}{2}$$

$$\Delta I_L = VOUT \times \frac{1 - \frac{VOUT}{VIN}}{L \times F_{SW}}$$

#### where

- ILOAD,MAX = Maximum output current

- △IL = Inductor current ripple

- Fsw = Switching frequency

- L = Inductor value

We recommend choosing the saturation current for the inductor 20% to 30% higher than the IL, MAX. A higher inductor value is also useful to lower ripple current but increases the transient response time as well. Selecting an inductor with low DCR provides better efficiency.

#### Input and Output Capacitor Selection

The architecture of the AW37420 allows use of tiny ceramic-type output capacitors with low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are thus recommended. To keep its resistance up to high frequencies and to achieve narrow capacitance variation with temperature, it is recommended to use X7R or X5R dielectric.

The input capacitor is the low impedance energy source for the converter that helps provide stable operation. A low ESR multilayer ceramic capacitor is recommended for best filtering. For most applications,10µF input capacitor is sufficient, a larger value reduces input voltage ripple.

The AW37420 is designed to operate with an output capacitor of 10µF to 22µF. A feed forward capacitor reduces the output ripple in PSM and improves the load transient response.

#### **Output Filter Design**

The inductor and the output capacitor together provide a low-pass filter for removing switching AC components and passing the DC voltage to the output. To simplify the seletion process, the following table outlines possible inductor and capacitor value combinations for most applications. Note that variations as high as +20% to -30% in the effective induance due to tolerances and saturation/derating is expected. Similarly, for the output capacitor output capacitor, due to tolerances and bias voltage derating the effictive capacitance can vary by +20% to -50%. For better performance and stability, a feed forward capacitor of 5pF should be used. Next table lists some suitable high frequency inductor and ceramic capacitor combinations that can be applied for most applications.

Some Suitable Combinations L and C Values for the LC Filter

| VOUT[V] | L[µH]          | C <sub>OUT</sub> [µF] |            |    |  |  |

|---------|----------------|-----------------------|------------|----|--|--|

| VO01[V] | <u> բլբույ</u> | 4.7                   | 10         | 22 |  |  |

|         | 0.47           |                       | ~          | ✓  |  |  |

| ≥1.2V   | 1              |                       | 44         | ✓  |  |  |

|         | 2.2            |                       | <b>✓</b> ✓ | ✓  |  |  |

|         | 0.47           |                       | ~          | ✓  |  |  |

| < 1.2V  | 1              |                       |            | ✓  |  |  |

|         | 2.2            |                       |            | ✓  |  |  |

Note: "

"

"

means more recommended for most applications."

For lower ripple at small output voltages ( < 1.2V) or use an inductor of  $2.2\mu H$ , a larger output capacitance is needed (at least  $22\mu F$ ).

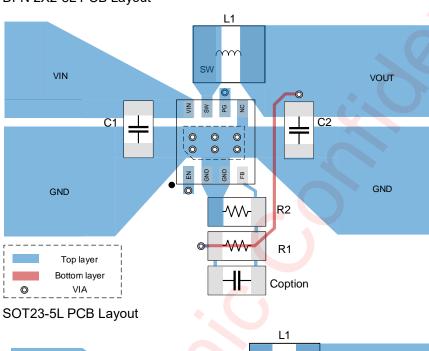

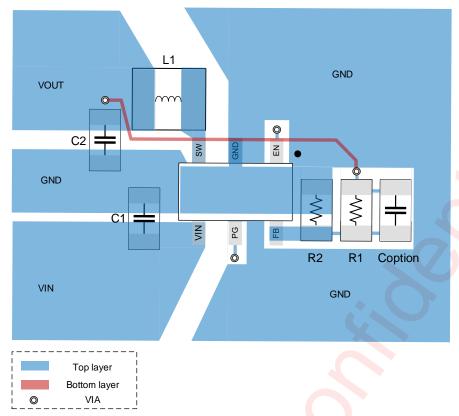

# **PCB Layout Consideration**

The input/output capacitors and the inductor should be placed as close as possible to the IC. This keeps the power traces short. Routing these power traces direct and wide results in low trace resistance and low parasitic inductance.

- The low side of the input and output capacitors must be connected properly to the GND pin to avoid a ground potential shift.

- The sense traces connected to FB is a signal trace. Special care should be taken to avoid noise being induced. Keep these traces away from SW nodes.

- A common ground should be used. GND layers might be used for shielding.

#### DFN 2X2-8L PCB Layout

#### SOT23-6L PCB Layout

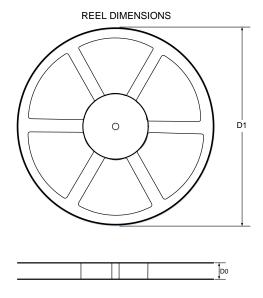

# **Tape And Reel Information**

**DFN 2X2-8L**

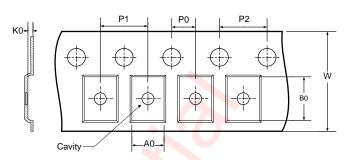

# TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

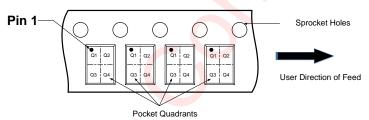

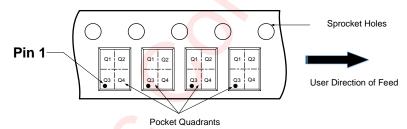

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### DIMENSIONS AND PIN1 ORIENTATION

| D1   | D0   | A0   | B0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant   |

|------|------|------|------|------|------|------|------|------|-----------------|

| (mm) | Fiiii Quadraiit |

| 178  | 8.4  | 2.3  | 2.3  | 1    | 2    | 4    | 4    | 8    | Q1              |

All dimensions are nominal

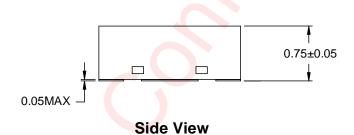

#### SOT23-6L and SOT23-5L

# REEL DIMENSIONS D1

#### TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### DIMENSIONS AND PIN1 ORIENTATION

| D1   | D0   |      | В0   | _    | P0   | P1   |      |      | Pin1 Quadrant  |  |

|------|------|------|------|------|------|------|------|------|----------------|--|

| (mm) | Fiiii Quadrant |  |

| 178  | 8.4  | 3.3  | 3.2  | 1.4  | 2    | 4    | 4    | 8    | Q3             |  |

All dimensions are nominal

# **Package Description**

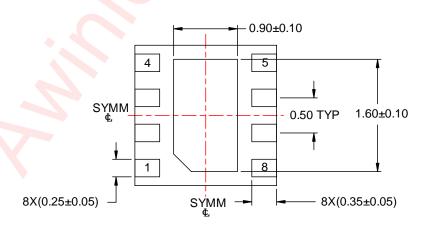

DFN 2X2-8L

**Bottom View**

Unit:mm

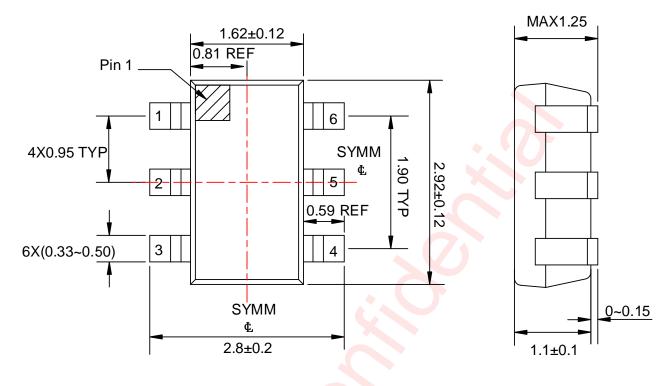

SOT23-6L

**Top View**

Unit: mm

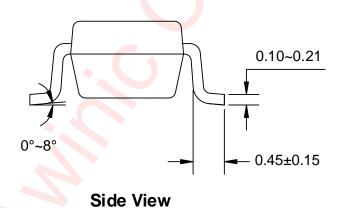

**Side View**

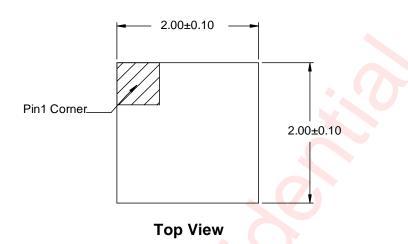

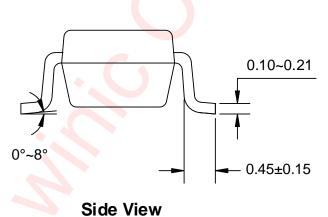

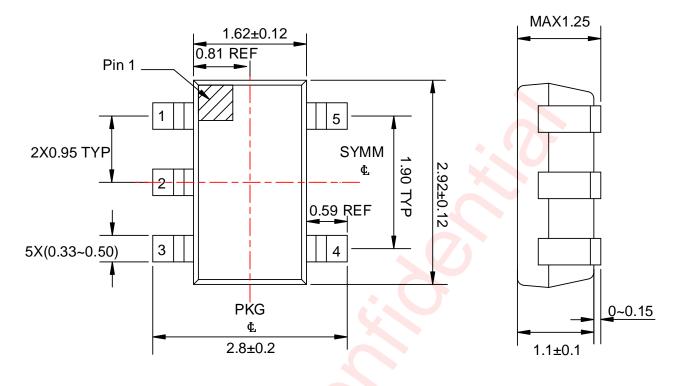

SOT23-5L

**Top View**

**Side View**

Unit: mm

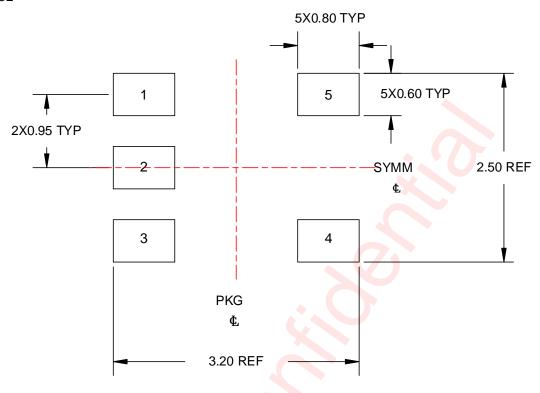

#### **Land Pattern Data**

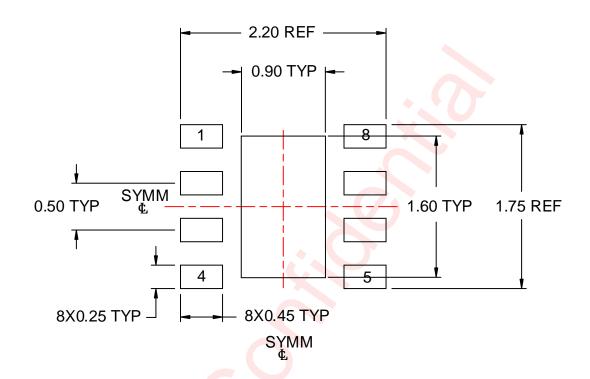

**DFN 2X2-8L**

Unit: mm

21

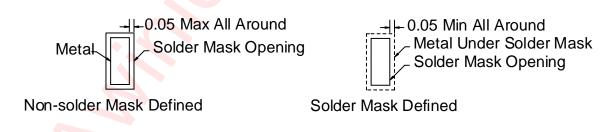

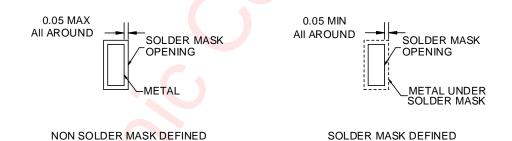

SOT23-6L

Unit: mm

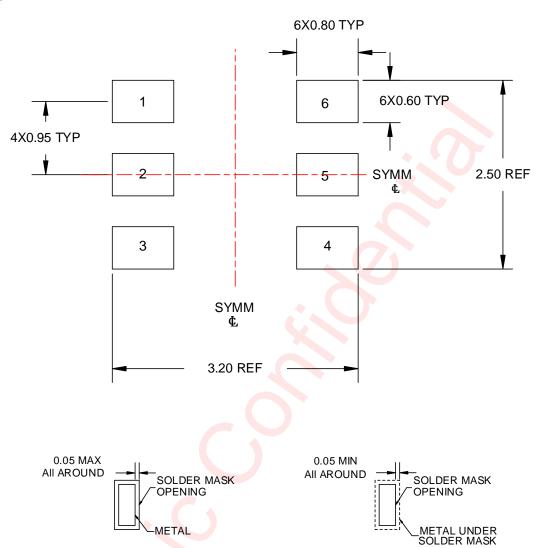

**SOLDER MASK DEFINED**

NON SOLDER MASK DEFINED

SOT23-5L

Unit: mm

# **Revision History**

| Version                                                                                                                                                            | Date      | Change Record                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------|

| V1.0                                                                                                                                                               | May 2023  | Datasheet V1.0 Released                                                         |

| V1.1 Jun. 2023  1. Modified the "AW37420" to "AW37420DNR and AW37420ASTR" in the chapter of Power Good.(P11) 2. Modified the chapter of Output Filter Design.(P13) |           | chapter of Power Good.(P11)                                                     |

| V1.2                                                                                                                                                               | Aug. 2024 | 1.Update the voltage range of 'VIN, EN, PG' from '-0.3V~6V' to '-0.3V~6.5V'(P5) |

#### **Disclaimer**

awinic

All trademarks are the property of their respective owners. Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.