## **OIS Close Loop Driver with Internal Hall Sensor**

#### **Features**

- Supply Voltage: 2.5V to 3.6V

- 2-wire Serial Interface(I<sup>2</sup>C)

- ◆ Support Private / Broadcast Communication

- ◆ Support Frequency Up to 3.4MHz

- ♦ Support 1.2V / 1.8V I2C Interface

- ◆ Support Automatic Address Recognition

- Built-in Constant Current Driver

- ♦ 12-bit DAC

- Built-in Hall Sensor

- ♦ Si Hall Sensor

- ♦ 8-level Hall Sensor Signal Amplification

- ◆ Support Hall Sensor Calibration

- Built-in 16bit A/D converter

- ♦ 14-bit Resolution

- ◆ Support Temperature and Hall Sampling

- Built-in 512 Bytes eFlash for User

- Built-in PID Controller

- ♦ PID Coefficients can be Specified by I2C

- ◆ Support Multi-scenes Application

- Filter Coefficients can be Specified by I<sup>2</sup>C

- Support Linearization Calibration

- Support Real-time Detection of Vibration Status

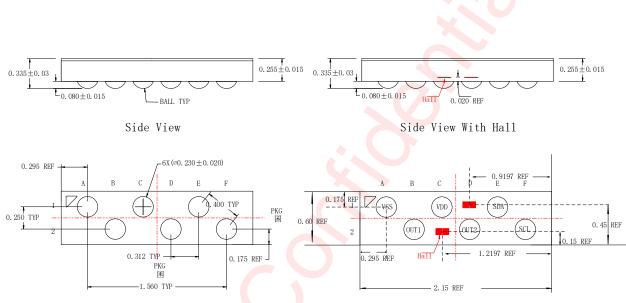

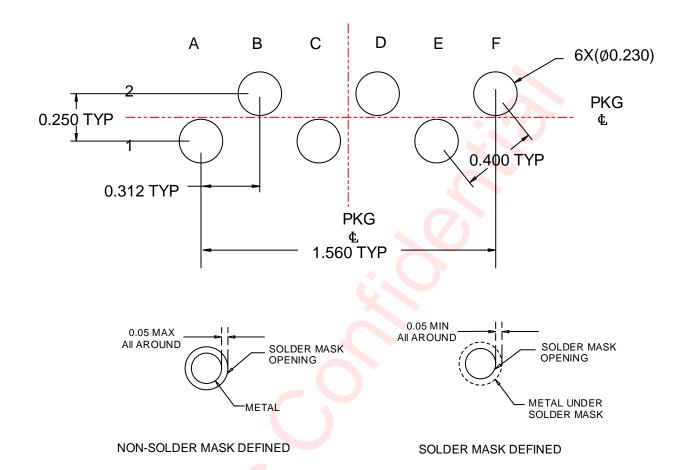

- Package

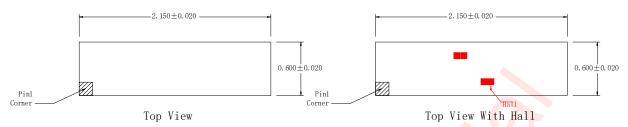

- ♦ WLCSP 0.600mm x 2.150mm x 0.335mm-6B

## **General Description**

AW86031 is an optical image stabilization (OIS) controller and close loop driver chip, which integrated a constant current driver. The default output current is ±150mA. The supply voltage range is from 2.5V to 3.6V.

AW86031 is controlled through the I<sup>2</sup>C serial interface that operates at clock rate up to 3.4MHz. The I<sup>2</sup>C device address can be configured by eFlash. The default address is 0xD8 (7-bit 0x6C).

AW86031 includes internal hall, 512 Bytes eFlash for user, digital PID controller, digital filter, A/D converter, D/A converter, and linearization calibration algorithm.

AW86031 can be used for auto focus or optical image stabilization applications in mobile cameras, digital cameras, camcorders, security cameras, web cameras and action cameras.

## **Applications**

Mobile Camera

Digital Camera

Camcorder

Security Camera

Web Camera and Action cameras

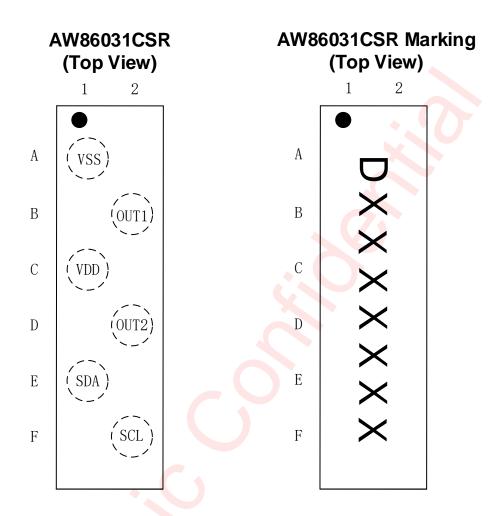

# **Pin Configuration And Top Mark**

D - AW86031CSR XXXXXXX - Production Tracing Code

Figure 1 AW86031 Pin Configuration And Top Mark

### **Pin Definition**

| No. | NAME | DESCRIPTION                            |

|-----|------|----------------------------------------|

| A1  | VSS  | Ground                                 |

| C1  | VDD  | Chip power supply                      |

| E1  | SDA  | I <sup>2</sup> C bus data input/output |

| B2  | OUT1 | H-bridge driver                        |

| D2  | OUT2 | H-bridge driver                        |

| F2  | SCL  | I <sup>2</sup> C bus clock input       |

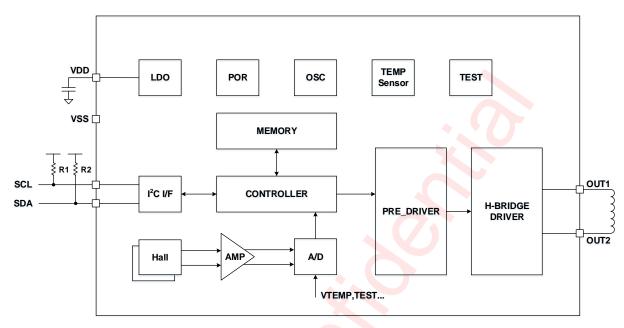

# **Functional Block Diagram**

Figure 2 AW86031 Function Block Diagram

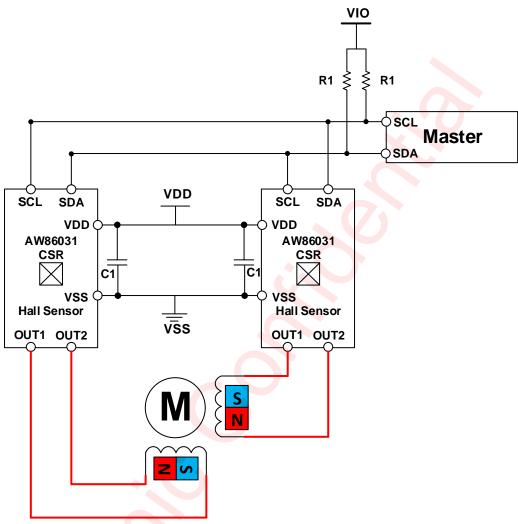

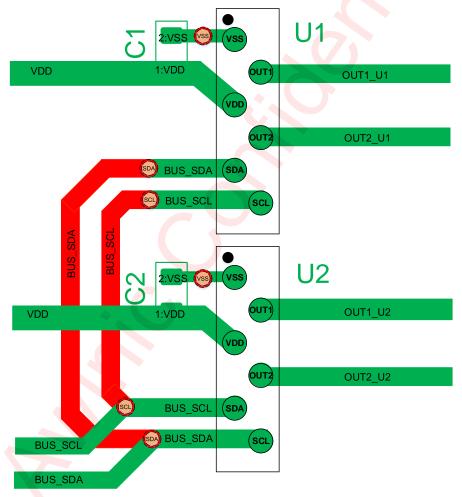

# **Typical Application Circuit**

Figure 3 Typical Application Circuit Of AW86031(NOTE1)

NOTE1: More details please refer to "Application Information" and "PCB Layout Consideration".

| Part Number | Temperature  | Package                                   | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-------------|--------------|-------------------------------------------|---------|----------------------------------|------------------------------|---------------------------------|

| AW86031CSR  | -40°C ~ 85°C | WLCSP<br>0.60mm x 2.15mm<br>x 0.335mm -6B | D       | MSL1                             | ROHS+HF                      | 4500 units/<br>Tape and<br>Reel |

## **Absolute Maximum Ratings**

| Parameters                                               | Range <sup>(NOTE2)</sup>                 |  |  |  |

|----------------------------------------------------------|------------------------------------------|--|--|--|

| Supply voltage range V <sub>DD</sub>                     | -0.3V to 4.2V                            |  |  |  |

| Control input voltage range V <sub>IN</sub>              | -0.3V to V <sub>DD</sub> +0.3V(MAX:4.2V) |  |  |  |

| Operating free-air temperature range TOPR                | -40°C to 85°C                            |  |  |  |

| Maximum operating junction temperature T <sub>JMAX</sub> | 150°C                                    |  |  |  |

| Storage temperature range T <sub>STG</sub>               | -55°C to 150°C                           |  |  |  |

| Lead temperature (soldering 10 seconds)                  | 280°C                                    |  |  |  |

| ESD <sup>(NOTE3)</sup>                                   |                                          |  |  |  |

| Test standard(HBM): ESDA/JEDEC JS-001-2017               | ±2000V                                   |  |  |  |

| Test standard(CDM): ESDA/JEDEC JS-002-2018               | ±1500V                                   |  |  |  |

| Test standard(MM): JESD22-A115C                          | ±400V                                    |  |  |  |

| Latch-up                                                 |                                          |  |  |  |

| Test standard: IESD79E                                   | +IT: 200mA                               |  |  |  |

| Test standard: JESD78E                                   | -IT: -200mA                              |  |  |  |

NOTE2: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE3: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

## **Recommended Operating Conditions**

| Parameters            | Symbol   | Min. | Тур. | Max. | Unit |

|-----------------------|----------|------|------|------|------|

| Power Supply Voltage  | $V_{DD}$ | 2.5  | 2.8  | 3.6  | ٧    |

| Control Input Voltage | Vin      | 0    |      | 3.6  | V    |

# **Electrical Characteristics**

V<sub>DD</sub>=2.8V, T<sub>A</sub>=25°C for typical values (unless otherwise noted)

| Parameter                      | Symbol   | Notes                            | Condition         | Min.       | Тур.     | Max. | Unit   | Applicable pins |

|--------------------------------|----------|----------------------------------|-------------------|------------|----------|------|--------|-----------------|

| 0 1                            | Idd      | Sleep Mode<br>(0x42[3] = 1)      | No Load           | 3          | 7        | 10   | μΑ     | •               |

| Supply<br>Current              | טטו      | Sleep Mode<br>(0x42[3] = 0)      | No Load           | 15         | 25       | 40   | μΑ     |                 |

|                                | loo      | Active Mode                      | No Load           | 3          | 6.8      | 9    | mA     |                 |

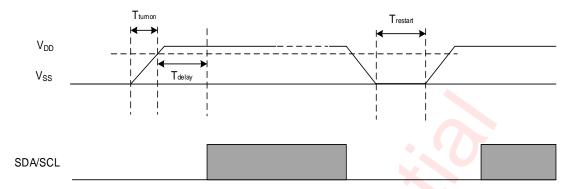

| Supply<br>Turn On<br>Time      | Tturnon  | (NOTE4)                          |                   | 0.05       |          | 3    | ms     |                 |

| Re-start<br>Time               | TRESTART | (NOTE5)                          |                   | 50         |          |      | ms     |                 |

| Turn On<br>Delay               | TDELAY   | (NOTE6)                          |                   | 0.5        |          |      | ms     |                 |

| -                              |          | DC Chara                         | acteristics: in   | put/outp   | ut level |      |        |                 |

| High-level<br>input<br>voltage | ViH      |                                  | CMOS<br>compliant | 0.84       |          |      | V      | SCL, SDA        |

| Low-level<br>input<br>voltage  | VIL      |                                  | Schmidt           |            |          | 0.36 | V      | SCL, SDA        |

| low-level<br>output<br>voltage | Vol      |                                  | loL= 20mA         | )          |          | 0.4  | V      | SDA             |

|                                |          | Drive                            | r Output Cha      | aracterist | ics      |      |        |                 |

| Output                         | IFULL    | Maximum current                  |                   | 140        | 150      | 160  | mA     |                 |

| Current                        | ILEAK    | Leakag <mark>e</mark><br>current |                   |            |          | 10   | μΑ     | OUT1,<br>OUT2   |

| Output On resistance           | Routres  | Resistance                       |                   |            | 2.5      |      | Ω      |                 |

|                                | ı        | eFlas                            | h Memory Ch       | aracteris  | tics     |      | 1      |                 |

| eFlash<br>Endurance            | FEN      |                                  |                   | 1000       |          |      | Cycles |                 |

| eFlash<br>Data<br>Retention    | Fre      |                                  |                   | 10         |          |      | Years  | Flash           |

| Program<br>time                | TPRO     |                                  |                   |            |          | 7.5  | μS     |                 |

| Erase time                     | TERASE   |                                  |                   |            |          | 4    | ms     |                 |

NOTE4: Start time of  $V_{DD}$  power up.

NOTE5: Restart time between power off and power on, and make sure power off reaches V<sub>SS</sub>.

NOTE6: 2-wire serial interface can operate delay time after power supply reaches 90% of the V<sub>DD</sub> level.

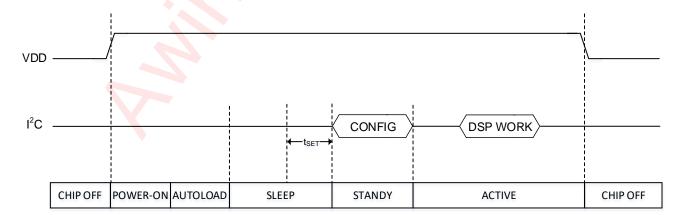

Figure 4 V<sub>DD</sub> Supply And I<sup>2</sup>C Interface Timing

7

## **Detailed Functional Description**

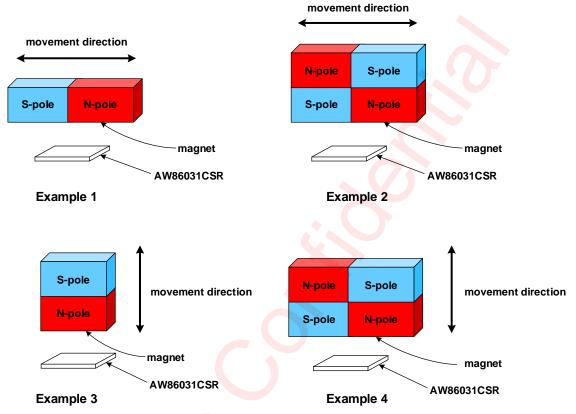

AW86031 is a close-loop driver chip which can detect the magnet position of Bi-directional voice coil motor(VCM) accurately. The example of magnet movement is shown in the figure below.

**Example Of Magnet Movement** Figure 5

### **Power-on Sequence**

Figure 6 Power-on Sequence

The power on sequence of this device is illustrated in the above figure. In this process, the memory data is automatically loaded into cache with CRC-check algorithm. The result of CRC-check (Address: 09h) can be accessed through I2C interface. At the end of auto-load operation, the device enters Sleep Mode. Mode-switch

上海艾为电子技术股份有限公司 hanghai awinic technology co., ltd.

can be realized by setting register CHIP MODE. The above figure is only one example of the cases what can happen after jumping from sleep. Setup waiting time (t<sub>SET</sub>) is needed when switching the device from Sleep Mode to Standby Mode or Active Mode.

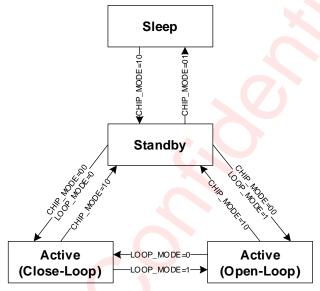

### **Operation Mode**

The device supports 3 operation modes, which are Sleep Mode, Standby Mode and Active Mode. Modes can be switched by configuring register CHIP\_MODE.

Figure 7 AW86031 Operation Mode

#### Sleep Mode

The device automatically enters the Sleep mode after power-on process or by setting register CHIP MODE to "2'b01". In this mode, I2C interface is accessible, while almost all circuits inside are not work for low power consumption. However, some registers related to scene-switch(1Eh~21h) and e512'(22h~32h) cannot be configured. The device will jump out of this mode when user sets register CHIP MODE to "2'b00" or "2'b10". It should be noted that there is a time delay from Sleep mode to Standby or Active mode. The delay time is about 400 µs.

#### Standby Mode

The device switches to Standby Mode by setting register CHIP\_MODE to "2'b10". The output of H-bridge is high-impedance in this mode, while all registers and memory data can be operated. The device will jump out of this mode when register CHIP\_MODE is set to "2'b00" or "2'b01".

#### **Active Mode**

The device can be set to Active Mode when register CHIP\_MODE is set to "2'b00". In this mode, VCM can be driven to the target position by H-bridge circuit. The register LOOP MODE is used to switch the Sub-Active Mode between Open-Loop Mode and Close-Loop Mode, the default setting is "1'b0" which means Close-Loop Mode.

### I<sup>2</sup>C Operation

This device supports the I²C serial bus and data transmission protocol in Fast-mode(Fm) at 400kHz, Fast-mode plus(Fm+) at 1MHz and High-speed mode (Hs-mode) at 3.4MHz. This device operates as a slave on the I²C bus. Connections to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k\sim10k\Omega$ . This device can support different high level (1.2V $\sim$ 3.3V) of this I²C interface.

#### **Device Address**

#### **Normal Mode**

The default device address is 0xD8(7-bit 0x6C), and which can be changed by eFlash memory, the permitted I<sup>2</sup>C addresses are any non-conflicting 7-bit value between 0x00 and 0x7F.

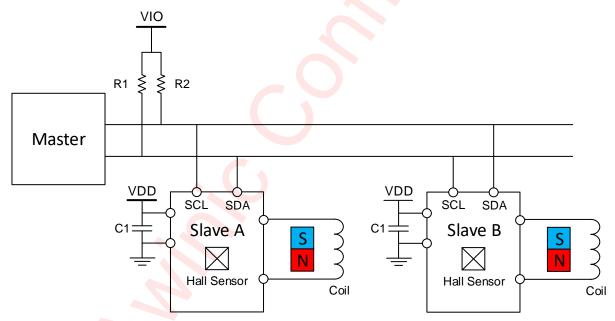

#### Self-Adapting Identification Mechanism

The device can self-adaptively identify and adjust the I<sup>2</sup>C interface and device address according to the hardware connection. As the connection method shown in the following figure, if the device address of Slave A is 0xD8(7-bit 0x6C), then the device address of Slave B is 0xDA(7-bit 0x6D), which means the LSB of the device address of Slave B takes the inverse logic.

Figure 8 Hardware Connection of Self-Adapting Identification

#### **Broadcast Mode**

The device supports broadcast mode, which is not available while broadcast address conflicts with device address. The default broadcast address is 0x00(7-bit 0x00), and which can be changed by eFlash memory, the permitted I<sup>2</sup>C addresses are any non-conflicting 7-bit value between 0x00 and 0x7F. The broadcast address is additionally used in advanced broadcast mode.

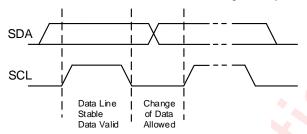

#### **Data Validation**

When SCL is high level, SDA level must be stable. SDA can be changed only when SCL is low level.

Figure 9 Data Validation Diagram

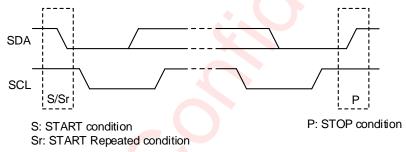

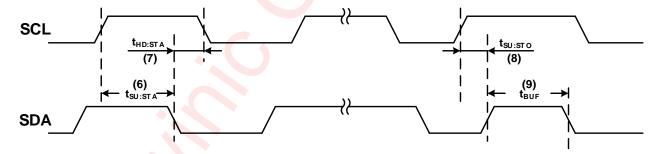

### I<sup>2</sup>C Start/Stop

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

Figure 10 I<sup>2</sup>C Start/Stop Condition Timing

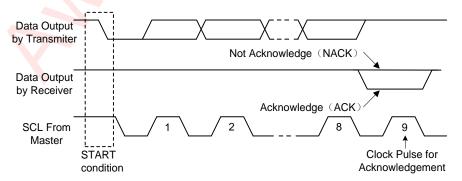

### Acknowledge(ACK)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends an 8-bit data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8-bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Figure 11 I<sup>2</sup>C ACK Timing

### Write Cycle

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a start condition, a number of byte transfers (set by the software) and a stop condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

Writing process refers to the master device write data into the slave device. In this process, the transfer direction of the data is always unchanged from the master device to the slave device. All acknowledgment bits are transferred by the slave device.

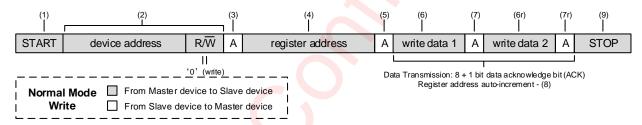

As shown in the figure below, the device supports three write modes: Normal Mode, Broadcast Mode, Advanced Broadcast Mode.

#### **Normal Mode**

As shown in the figure below, the transmission process follows the steps below:

Figure 12 Normal Mode Write Cycle

- (1) Master device generates START condition to indicate write cycle start.

- (2) Master device transmits 7-bits device address and followed by the "read/write" flag ( $R/\overline{W} = 0$ ).

- (3) Slave device transmits an acknowledgment bit (ACK) to confirm whether the device address is correct.

- (4) Master device transmits 8-bits register address.

- (5) Slave device transmits an acknowledgment bit (ACK) to confirm whether the register address is correct.

- (6) Master device transmits 8-bits write data to the register which needs to be written.

- (7) Slave device transmits an acknowledgment bit (ACK) to confirm whether the data is sent successfully.

- (8) If master device needs to continue transmitting data, just need to repeat the step 6~7, the following data will adaptively enter burst transmission, which means the corresponding register address will auto-increment.

- (9) Master device generates STOP condition to indicate write cycle end.

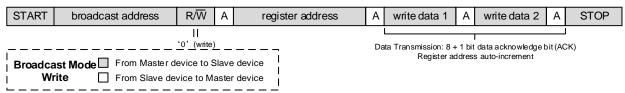

#### **Broadcast Mode**

The transmission process follows the figure below:

Figure 13 Broadcast Mode Write Cycle

The only difference from Normal Mode is that the device address is replaced by the broadcast address, so that all slaves which respond broadcast call will receive the same write data.

#### **Setup Method**

Broadcast mode is available after completing the following configuration. As shown in figure xx, if the hardware connection of slave A is defined as positive, then slave B is negative:

| Slave | Connection | Sequence | Device<br>Address. | Register<br>Address. | Register<br>Data | Description                                              |                                                |

|-------|------------|----------|--------------------|----------------------|------------------|----------------------------------------------------------|------------------------------------------------|

|       | A positive | 1        | 0xD8               | 0x54                 | 0x49             | Set to improve the stability of multi-<br>device linkage |                                                |

| А     |            | positive | 2                  | 0xD8                 | 0x55             | 0xFF                                                     | Set to configure write cycle data burst length |

|       |            | 3        | 0xD8               | 0x57                 | 0x01             | Set to configure data burst slot of each slave           |                                                |

|       |            | 1        | 0xDA               | 0x54                 | 0x46             | Set to improve the stability of multi-<br>device linkage |                                                |

| В     | negative   | 2        | 0xDA               | 0x55                 | 0xFF             | Set to configure write cycle data burst length           |                                                |

|       |            | 3        | 0xDA               | 0x57                 | 0x01             | Set to configure data burst slot of each slave           |                                                |

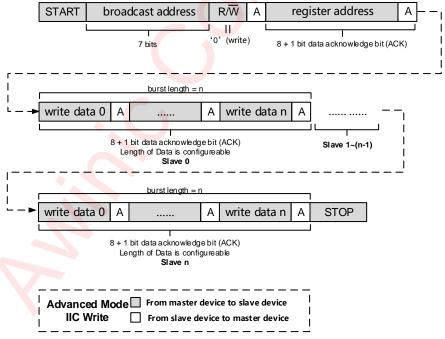

#### **Advanced Broadcast Mode**

The transmission process follows the figure below:

Figure 14 Advanced Broadcast Mode Write Cycle

#### Setup Method

Advanced broadcast mode is available after completing the following configuration. As shown in figure xx, if the hardware connection of slave A is defined as positive, then slave B is negative. For example, the host needs to send a total of 4 bytes write data if it is assumed that the TARGET registers of two devices are driven synchronously.

| Slave | Connection | Sequence | Device<br>Address | Register<br>Address. | Register<br>Data                            | Description                                              |

|-------|------------|----------|-------------------|----------------------|---------------------------------------------|----------------------------------------------------------|

|       |            | 1        | 0xD8              | 0x54                 | Set to improve the stability device linkage |                                                          |

| А     | A positive | 2        | 0xD8              | 0x55                 | 0x02                                        | Set to configure write cycle data burst length           |

|       |            | 3        | 0xD8              | 0x57                 | 0x01                                        | Set to configure data burst slot of each slave           |

|       |            | 1        | 0xDA              | 0x54                 | 0x46                                        | Set to improve the stability of multi-<br>device linkage |

| В     | negative   | 2        | 0xDA              | 0x55                 | 0x02                                        | Set to configure write cycle data burst length           |

|       |            | 3        | 0xDA              | 0x57                 | 0x02                                        | Set to configure data burst slot of each slave           |

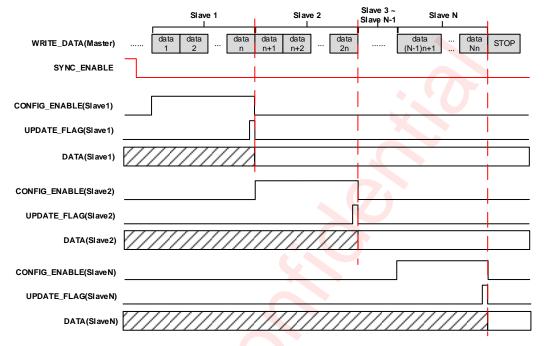

#### Data Update Mechanism - Real-Time Mode

Real-time mode is one of the data update mechanism supported by the device in advanced broadcast mode. Each slave will automatically update the data after writing data matching the configured data burst length.

Figure 15 Real-Time Update

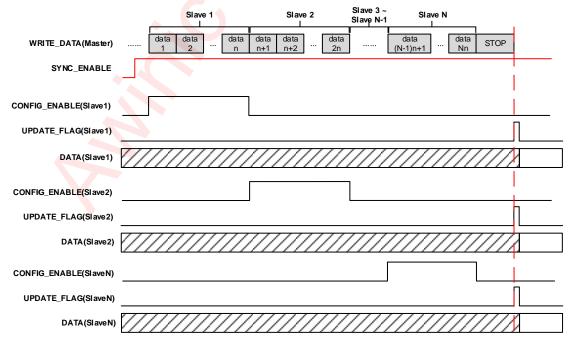

#### Data Update Mechanism - Synchronous Mode

Synchronous mode is one of the data update mechanism supported by the device in advanced broadcast mode. All slaves will automatically update the data after writing a complete data stream and generating a STOP flag.

Figure 16 Synchronous Update

上海艾为电子技术股份有限公司 shanghai awinis technology so... Itd

### **Read Cycle**

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a start condition, a number of byte transfers (set by the software) and a stop condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

Reading process refers to the slave device reading data back to the master device. In this process, the direction of data transmission will change. The master device sends START state and slave address twice, and sends the opposite "read/write" flag after the change. Meanwhile, acknowledgment bits are transferred by the master device after the change.

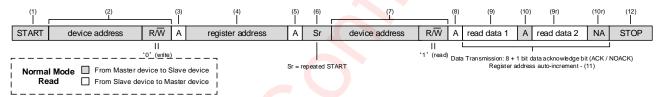

As shown in the figure below, the device supports two read modes: Normal Mode, Advanced Broadcast Mode.

#### **Normal Mode**

As shown in the figure below, the transmission process follows the steps below:

Figure 17 Normal Mode Read Cycle

- (1) Master device generates START condition to indicate write cycle start.

- (2) Master device transmits 7-bits device address and followed by the "read/write" flag ( $R/\overline{W} = 0$ ).

- (3) Slave device transmits an acknowledgment bit (ACK) to confirm whether the device address is correct.

- (4) Master device transmits 8-bits register address.

- (5) Slave device transmits an acknowledgment bit (ACK) to confirm whether the register address is correct.

- (6) Master device generates repeated START condition to indicate read cycle start.

- (7) Master device transmits 7-bits device address and followed by the "read/write" flag ( $R/\overline{W} = 1$ ).

- (8) Slave device transmits an acknowledgment bit (ACK) to confirm whether the device address is correct.

- (9) Slave device transmits 8-bits read data from the register which needs to be read.

- (10)Master device transmits an acknowledgment bit (ACK) to confirm whether the data is sent successfully. Specially, it is not necessary to acknowledge the last data, which means a non-acknowledgment (NOACK) is acceptable.

- (11)If slave device needs to continue transmitting data, just need to repeat the step 9~10, the following data will adaptively enter burst transmission, which means the corresponding register address will auto-increment.

- (12) Master device generates STOP condition to indicate read cycle end.

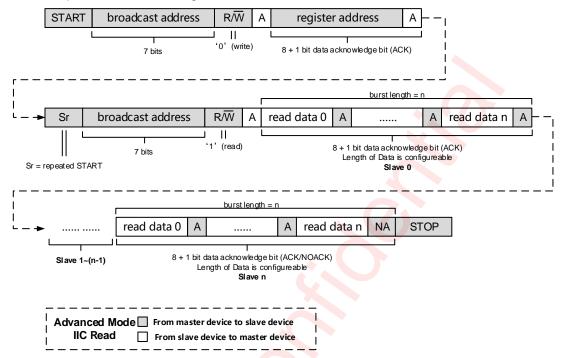

#### **Advanced Broadcast Mode**

The transmission process follows the figure below:

Figure 18 Advanced Broadcast Mode Read Cycle

### **Setup Method**

Advanced broadcast mode is available after completing the following configuration. As shown in figure xx, if the hardware connection of slave A is defined as positive, then slave B is negative. For example, the host needs to receive a total of 12 bytes read data if it is assumed that the ADC\_CH registers of two devices needs to be returned.

| Slave | Connection | Sequence | Device<br>Address. | Register<br>Address. | Register<br>Data | Description                                              |

|-------|------------|----------|--------------------|----------------------|------------------|----------------------------------------------------------|

|       | positive   | 1        | 0xD8               | 0x54                 | 0x49             | Set to improve the stability of multi-<br>device linkage |

| А     |            | 2        | 0xD8               | 0x56                 | 0x06             | Set to configure read cycle data burst length            |

|       |            | 3        | 0xD8               | 0x57                 | 0x01             | Set to configure data burst slot of each slave           |

|       |            | 1        | 0xDA               | 0x54                 | 0x46             | Set to improve the stability of multi-<br>device linkage |

| В     | negative   | 2        | 0xDA               | 0x56                 | 0x06             | Set to configure read cycle data burst length            |

|       |            | 3        | 0xDA               | 0x57                 | 0x02             | Set to configure data burst slot of each slave           |

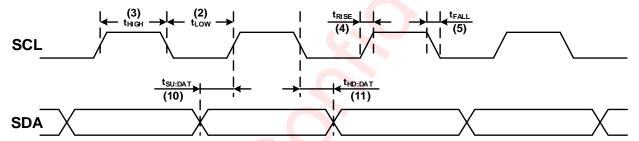

### **Timing Feature**

|     |                     | Parameter                                | F    | m    | Fr   | n+   | Hs-mode |      | Unit  |

|-----|---------------------|------------------------------------------|------|------|------|------|---------|------|-------|

| No. | Symbol              | Name                                     | Min  | Max  | Min  | Max  | Min     | Max  | Ollit |

| 1   | fscL                | SCL Clock frequency                      |      | 400  |      | 1000 |         | 3400 | KHz   |

| 2   | t <sub>LOW</sub>    | SCL Low level Duration                   | 1.30 |      | 0.50 |      | 0.16    |      | μs    |

| 3   | t <sub>HIGH</sub>   | SCL High level Duration                  | 0.60 |      | 0.26 |      | 0.06    |      | μs    |

| 4   | trise               | SCL, SDA rise time                       |      | 0.30 |      | 0.12 |         | 0.04 | μs    |

| 5   | t <sub>FALL</sub>   | SCL, SDA fall time                       |      | 0.30 |      | 0.12 |         | 0.04 | μs    |

| 6   | tsu:sta             | Setup time SCL to START state            | 0.60 |      | 0.26 |      | 0.16    |      | μs    |

| 7   | thd:sta             | (repeat-start) start condition hold time | 0.60 |      | 0.26 |      | 0.16    |      | μs    |

| 8   | tsu:sto             | Stop condition setup time                | 0.60 |      | 0.26 |      | 0.16    |      | μs    |

| 9   | t <sub>BUF</sub>    | Time between start and stop condition    | 1.30 |      | 0.50 |      | 0.16    |      | μs    |

| 10  | t <sub>SU:DAT</sub> | SDA setup time                           | 0.10 |      | 0.05 |      | 0.01    |      | μs    |

| 11  | thd:dat             | SDA hold time                            | 0    | 0.90 | 0    | 0.45 | 0       | 0.07 | μs    |

Figure 19 SCL and SDA timing relationships in the data transmission process

Figure 20 The timing relationship between START and STOP state

#### eFlash

The storage space of eFlash is 2K bytes and 512 bytes of them is available for users. eFlash data can automatically loaded into cache during power-on process and can also be refreshed with the data in cache. It supports self-check, erase-program-protection and data backup for critical area. ACC\_FLS\_KEY and ACC\_CAC\_KEY must be unlocked before operating eFlash. Besides, one-click-programming operation is available in addition to the normal functions.

#### **Erase Operation**

The sector/block erase operation allows the system to erase the eFlash on sector-by-sector or block-by-block. The sector architecture is based on uniform sector size of 64 bytes. The block size is 128 bytes. The protection must be unlock before erasing the critical area.

#### **Program Operation**

It is necessary to erase the area which need to be refreshed before programing eFlash. The mapping relationship between eFlash and cache should be pre-configured as well. The protection must be unlock before programming the critical area. One-click-programming operation, which based on the program operation, is an extension feature of the device.

#### Read Operation

There are two types of reading operation, normal read and self-check read. Normal read means reading the data in eFlash without the CRC-check. Self-check read is just the opposite. Before self-check read, the CRC checking code should be programmed into eFlash along with the data to be verified.

### **DSP System**

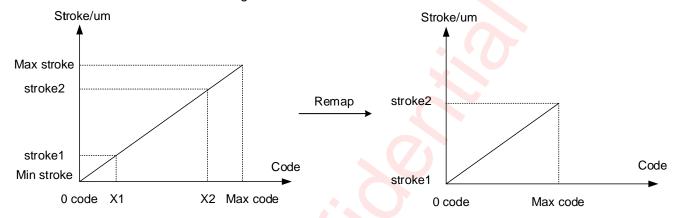

### **Remapping Function**

The purpose of remapping function is to form a mapping relationship between the target code and stroke. The gain value and the offset value can be configured via I<sup>2</sup>C based on the motor characteristics.

Figure 21 Remapping Function

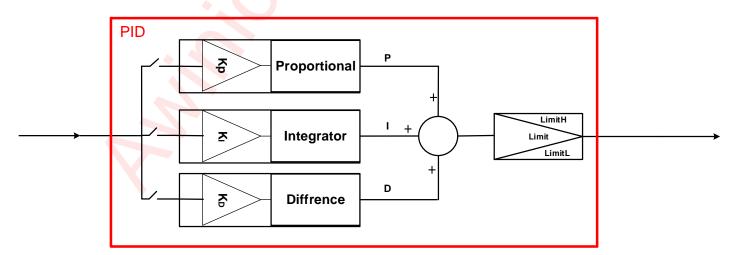

#### **PID Control**

In order to realize the quick stabilization of the motor, there is a built-in PID algorithm circuit in AW86031. It supports the output limiting function and the branch P, I and D parameters are dynamically configurable. In order to increase the stability of the motor, the output of PID can be frozen through the I<sup>2</sup>C interface. Besides, the output of PID can also be closed for ball motor to reduce power consumption. The PID algorithm circuit is shown in the figure below.

Figure 22 PID Typical Diagram

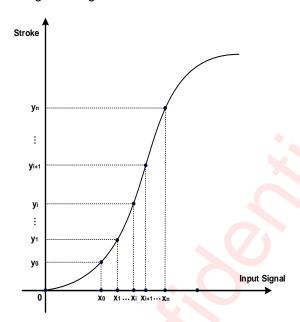

### **Linearization Calibration**

The device IC supports linearization calibration ,which is carried out through a straight line fitted by the input

signal and VCM stroke. The following is a diagram of this mode.

Figure 23 The Linearization Calibration Mode

### **Protection Mechanism**

### **Over Current Protection (OCP)**

This protection function is triggered when the current of any output tube is beyond the pre-set threshold. The output stages will be shut down to prevent damage to itself. After a configurable delay, the output stages of device will restart and the current protection circuit will keep on monitoring as well. The register CHIP\_STATUS[5] – OC is accessible to users to monitor this status.

# **Register Configuration**

# Register List<sup>(NOTE7)</sup>

| ADDR | NAME             | R/W | Bit7           | Bit6                                                                 | Bit5                       | Bit4          | Bit3         | Bit2      | Bit1        | Bit0        | Default |

|------|------------------|-----|----------------|----------------------------------------------------------------------|----------------------------|---------------|--------------|-----------|-------------|-------------|---------|

| 0x00 | TARGET0          | RW  |                |                                                                      |                            | TARGH         | l            |           |             |             | 0x80    |

| 0x01 | TARGET1          | RW  |                |                                                                      | TARGL                      |               |              |           |             |             | 0x00    |

| 0x02 | MODE_CTRL        | RW  |                | CHIP                                                                 | _MODE                      |               |              |           |             | LOOP_MODE   | 0x20    |

| 0x03 | WORK_EN          | RW  |                |                                                                      | _                          | SYNC_TRIG_OFF |              |           | =           | WORK_EN     | 0x01    |

| 0x05 | CRC_STATUS0      | RO  |                |                                                                      |                            | CRC_STAT      |              |           |             |             | 0x00    |

| 0x06 | CRC_STATUS1      | RO  |                |                                                                      |                            | CRC_STAT      |              |           |             |             | 0x00    |

| 0x07 | CRC_STATUS2      | RO  |                |                                                                      |                            | CRC_STAT      |              |           |             |             | 0x00    |

| 0x08 | CRC_STATUS3      | RO  |                |                                                                      |                            | CRC_STAT      |              |           |             |             | 0x00    |

| 0x09 | CRC_STATUS4      | RO  |                |                                                                      | 1                          | CRC_STAT      | US4          |           |             | •           | 0x00    |

| 0x0A | CHIP_STATUS      | RW  |                |                                                                      | OC                         | _             | _            |           | _           | _           | 0x00    |

| 0x0B | PID_STATUS       | RW  | PID_DONE       | PID_BUSY                                                             | P_OVFL                     | P_UDFL        | D_OVFL       | D_UDFL    | PID_OVFL    | PID_UDFL    | 0x00    |

| 0x0C | AFE_STATUS       | RW  | AFE_BUSY       | _                                                                    | HALL_DIV_DIV0              | AFE_ERR       | AFE_TIME_OUT |           | ADC_CUR_CH  |             | 0x00    |

| 0x0D | ADC_CH0H         | RO  |                |                                                                      |                            | ADC_CHO       |              |           |             |             | 0x00    |

| 0x0E | ADC_CH0L         | RO  |                |                                                                      |                            | ADC_CH        |              |           |             |             | 0x00    |

| 0x0F | ADC_CH1H         | RO  |                |                                                                      |                            | ADC_CH1       |              |           |             |             | 0x00    |

| 0x10 | ADC_CH1L         | RO  |                |                                                                      |                            | ADC_CH        |              |           |             |             | 0x00    |

| 0x11 | ADC_CH2H         | RO  |                |                                                                      |                            | ADC_CH2       |              |           |             |             | 0x00    |

| 0x12 | ADC_CH2L         | RO  |                |                                                                      |                            | ADC_CH        |              |           |             |             | 0x00    |

| 0x13 | EIS_OUTH         | RO  |                |                                                                      |                            | EIS_OUT       |              |           |             |             | 0x10    |

| 0x14 | EIS_OUTL         | RO  |                |                                                                      |                            | EIS_OUT       |              |           |             |             | 0x00    |

| 0x15 | DRV_OUTH         | RO  |                |                                                                      |                            | DRV_OU        | TH           |           |             |             | 0x08    |

| 0x16 | DRV_OUTL         | RO  |                |                                                                      |                            | DRV_OU        |              |           |             |             | 0x00    |

| 0x1E | SCSR             | RW  | AUTO_SCSW_EN   | DIRECT_JUMP                                                          | SCSW2FLS_BUSY              | SCSW2FLS_HIS  | SCSW2FLS_CUR | VIBRATING | CONVERGED   | REVIBRATE   | 0x00    |

| 0x1F | SCSTCNTH         | RO  |                |                                                                      |                            | SCSTCNT       |              |           |             |             | 0x00    |

| 0x20 | SCSTCNTL         | RO  |                | SCSTENTL SCSTENTL                                                    |                            |               |              |           |             | 0x00        |         |

| 0x21 | ERGDR            | RW  | SC             | SCSW_AUTO_JUMPDIR ERGD_BYPASS ERGD_MAN_JUMPDIR ERGD_DONE ERGD_BYPASS |                            |               |              |           |             | 0x01        |         |

| 0x22 | SCSWCR           | RW  |                | SCSWCR                                                               |                            |               |              |           |             | 0x00        |         |

| 0X23 | ACC_FLS_KEY      | RW  |                | ACC_FLS_KEY                                                          |                            |               |              |           |             | 0x00        |         |

| 0X24 | ACC_CAC_KEY      | RW  |                |                                                                      |                            | ACC_CAC_      |              |           |             |             | 0x00    |

| 0X26 | WP_UNLOCK        | RW  |                |                                                                      |                            | WP_UNLC       | OCK          |           |             |             | 0x00    |

| 0x27 | ОСРО             | RW  |                |                                                                      |                            | ОСРО          | ı            |           |             |             | 0x00    |

| 0x28 | EFLASH_ADDR0     | RW  | BDGFLSNVR      |                                                                      |                            |               |              | BDGFL     | SADDR0      |             | 0x00    |

| 0x29 | EFLASH_ADDR1     | RW  |                |                                                                      |                            | BDGFLSAD      | DR1          |           |             |             | 0x00    |

| 0x2A | EFLASH_MAP0      | RW  |                |                                                                      |                            |               |              | ISPFL     | SMAP0       |             | 0x00    |

| 0x2B | EFLASH_MAP1      | RW  |                |                                                                      |                            | ISPFLSMA      |              |           |             |             | 0x00    |

| 0x2C | CACHE_MAP        | RW  |                |                                                                      |                            | CACMA         | P            |           |             |             | 0x00    |

| 0x2D | CMD_WORD_LEN     | RW  |                |                                                                      |                            | ISPWL         | I            | 1 -       | 1           | 1           | 0x3F    |

| 0x2E | EFLASH_CFG       | RW  | ISP_TESTEN     | ISP_DPSTB_EN                                                         | I <mark>SP</mark> _MAIN_EN | ISP_NVR_EN    | ISP_BLOCK    | ISP_NVR   | ISP_CHIP    | ISP_EN      | 0x60    |

| 0x2F | CMD              | RW  |                |                                                                      |                            |               |              | ISP_      | CMD         |             | 0x08    |

| 0x30 | CMD_GO           | RW  |                |                                                                      |                            | ISP_G0        |              |           | _           | _           | 0x00    |

| 0x31 | EFLASH_STATUS    | RO  | ISP_WP_ERROR   | ISP_WP_OK                                                            | ISP_CMD_BUSY               | WKUP_DONE     | TRIM_DONE    | AUTO_DONE | FLTLIN_DONE | INIT_DONE   | 0x00    |

| 0x32 | FLS_T_PGS_WUP    | RW  | -              |                                                                      |                            | FLS_T_PGS_    |              |           |             |             | 0x35    |

| 0x33 | FLS_DOUT0        | RO  | _              |                                                                      |                            | FLS_DOUT(     |              |           |             |             | 0x00    |

| 0x34 | FLS_DOUT1        | RO  |                |                                                                      |                            | FLS_DOUT1     |              |           |             |             | 0x00    |

| 0x35 | FLS_DOUT2        | RO  |                |                                                                      |                            | FLS_DOUT2     |              |           |             |             | 0x00    |

| 0x36 | FLS_DOUT3        | RO  |                |                                                                      |                            | FLS_DOUT3     |              |           |             |             | 0x00    |

| 0x37 | RESERVEDO        | RW  |                |                                                                      |                            | RESERVEI      |              |           |             |             | 0x00    |

| 0x38 | CHIP_ID<br>TRIM0 | RO  |                |                                                                      |                            | CHIP_II       |              |           |             |             | 0x79    |

| 0x42 |                  | RW  |                |                                                                      |                            | DCAC 51       | VBG_SEL      |           |             |             | 0x0C    |

| 0x50 | PCAC_FLAG        | RW  | WORK EN CAC    | CIUE :                                                               | AODE CAC                   | PCAC_FL/      |              | 1         | I FIG CEL   | LINICE      | 0xFF    |

| 0x51 | MODCTRCR         | RW  | WORK_EN_CAC    | CHIP_N                                                               | MODE_CAC                   | DSP_GATE_EN   | LIN_BYPASS   |           | EIS_SEL     | LIN_SEL     | 0xA8    |

| 0x52 | DEVADDR          | RW  |                |                                                                      |                            |               | DEV_ADDR     |           |             |             | 0x6C    |

| 0x53 | GNRADDR          | RW  | TELACIT NO EV. | EN CND ACT                                                           | DELAY CEL                  | DEC CEI       | GNR_ADDR     | SCI CEI   | DOC CTD OFF | NEC CER OFF | 0x00    |

| 0x54 | IIC_CFG          | RW  | EFLASH_IIC_EN  | EN_GNR_ACK                                                           | DELAY_SEL                  | DEG_SEL       | SDA_SEL      | SCL_SEL   | POS_CTR_OFF | NEG_CTR_OFF | 0x40    |

| 0x55 | BURST_LEN_W      | RW  |                |                                                                      |                            | CFG_BURST_I   |              |           |             |             | 0xFF    |

| 0x56 | BURST_LEN_R      | RW  |                |                                                                      |                            | CFG_BURST_    | LEIN_K       | 050.00    | OT NUMA     |             | 0xFF    |

| 0x57 | BURST_SLOT       | RW  |                |                                                                      | _                          |               |              | CFG_SLI   | DT_NUM      |             | 0x01    |

NOTE7: eFlash cache registers are identified with a green background.

# **Register Detailed Description**

| TAI | TARGET0: (Address 00h) Target Register High Part |    |                                                 |      |  |  |  |  |

|-----|--------------------------------------------------|----|-------------------------------------------------|------|--|--|--|--|

| Bit | it Symbol R/W Description Def                    |    |                                                 |      |  |  |  |  |

| 7:0 | TARGH                                            | RW | 13-bits Target Register High Part :Target[12:5] | 0x80 |  |  |  |  |

| TARG | TARGET1: (Address 01h) Target Register Low Part |     |                                                |         |  |  |  |

|------|-------------------------------------------------|-----|------------------------------------------------|---------|--|--|--|

| Bit  | Symbol                                          | R/W | Description                                    | Default |  |  |  |

| 7:3  | TARGL                                           | RW  | 13-bits Target Register Low Part : Target[4:0] | 0x00    |  |  |  |

| 2:0  | RESERVED                                        | RW  | Reserved                                       | 0x0     |  |  |  |

| Bit | Symbol    | R/W | Description                                                                                         | Default |

|-----|-----------|-----|-----------------------------------------------------------------------------------------------------|---------|

| 7   | RESERVED  | RW  | Reserved                                                                                            | 0x0     |

| 6:5 | CHIP_MODE | RW  | Chip Mode Switch b00: Active mode b01: Sleep mode(PD mode, default) b10: Standby mode b11: Reserved | 0x1     |

| 4:1 | RESERVED  | RW  | Reserved                                                                                            | 0x0     |

| 0   | LOOP_MODE | RW  | Loop Mode Switch 0: Close Loop 1: Open Loop                                                         | 0x0     |

| Bit | Symbol        | R/W | Description                                                   | Default |

|-----|---------------|-----|---------------------------------------------------------------|---------|

| 7:5 | RESERVED      | RW  | Reserved                                                      | 0x0     |

| 4   | SYNC_TRIG_OFF | RW  | Target Data Synchronous Trigger 0: Enable(default) 1: Disable | 0x0     |

| 3:1 | RESERVED      | RW  | Reserved                                                      | 0x0     |

| 0   | WORK_EN       | RW  | Active Mode Work Enable 0: Disable 1: Enable                  | 0x1     |

| CRC | _STATUS0: (Address 05h) CF | RC Data F | egister Page0                    |         |

|-----|----------------------------|-----------|----------------------------------|---------|

| Bit | Symbol                     | R/W       | Description                      | Default |

| 7:0 | CRC_STATUS0                | RO        | CRC Data Register Page0 [8*4+:8] | 0x00    |

| CRC | CRC_STATUS1: (Address 06h) CRC Data Register Page1 |     |                                  |         |  |  |  |

|-----|----------------------------------------------------|-----|----------------------------------|---------|--|--|--|

| Bit | Symbol                                             | R/W | Description                      | Default |  |  |  |

| 7:0 | CRC_STATUS1                                        | RO  | CRC Data Register Page1 [8*3+:8] | 0x00    |  |  |  |

| CRC | CRC_STATUS2: (Address 07h) CRC Data Register Page2 |     |                                  |         |  |  |  |

|-----|----------------------------------------------------|-----|----------------------------------|---------|--|--|--|

| Bit | Symbol                                             | R/W | Description                      | Default |  |  |  |

| 7:0 | CRC_STATUS2                                        | RO  | CRC Data Register Page2 [8*2+:8] | 0x00    |  |  |  |

| C | CRC_STATUS3: (Address 08h) CRC Data Register Page3 |             |     |                                  |         |  |  |

|---|----------------------------------------------------|-------------|-----|----------------------------------|---------|--|--|

| В | Bit                                                | Symbol      | R/W | Description                      | Default |  |  |

| 7 | :0                                                 | CRC_STATUS3 | RO  | CRC Data Register Page3 [8*1+:8] | 0x00    |  |  |

| CRC | CRC_STATUS4: (Address 09h) CRC Data Register Page4 |     |                                  |         |  |

|-----|----------------------------------------------------|-----|----------------------------------|---------|--|

| Bit | Symbol                                             | R/W | Description                      | Default |  |

| 7:0 | CRC_STATUS4                                        | RO  | CRC Data Register Page4 [8*0+:8] | 0x00    |  |

|     |                                                    |     |                                  |         |  |

| CHIP | CHIP_STATUS: (Address 0Ah) Chip Status Register |     |                                                           |         |  |  |  |

|------|-------------------------------------------------|-----|-----------------------------------------------------------|---------|--|--|--|

| Bit  | Symbol                                          | R/W | Description                                               | Default |  |  |  |

| 7:6  | RESERVED                                        | RW  | Reserved                                                  | 0x0     |  |  |  |

| 5    | ос                                              | RW  | Over Current Flag Access CHIP_STATUS to Clear the OC Flag | 0x0     |  |  |  |

| 4:0  | RESERVED                                        | RW  | Reserved                                                  | 0x0     |  |  |  |

| PID_ | PID_STATUS: (Address 0Bh) PID Status Register |     |                                                                          |         |  |  |

|------|-----------------------------------------------|-----|--------------------------------------------------------------------------|---------|--|--|

| Bit  | Symbol                                        | R/W | Description                                                              | Default |  |  |

| 7    | PID_DONE                                      | RO  | PID Controller Work Done                                                 | 0x0     |  |  |

| 6    | PID_BUSY                                      | RO  | PID Controller Work Busy                                                 | 0x0     |  |  |

| 5    | P_OVFL                                        | RWC | Factor P Overflow Flag<br>Write 1 to Clear The Factor P Saturation Flag  | 0x0     |  |  |

| 4    | P_UDFL                                        | RWC | Factor P Underflow Flag<br>Write 1 to Clear The Factor P Saturation Flag | 0x0     |  |  |

| 3    | D_OVFL                                        | RWC | Factor D Overflow Flag<br>Write 1 to Clear The Factor D Saturation Flag  | 0x0     |  |  |

| 2    | D_UDFL                                        | RWC | Factor P Underflow Flag<br>Write 1 to Clear The Factor D Saturation Flag | 0x0     |  |  |

| 1 | PID_OVFL | RWC | PID Controller Output Overflow<br>Write 1 to Clear The PID Saturation Flag  | 0x0 |

|---|----------|-----|-----------------------------------------------------------------------------|-----|

| 0 | PID_UNFL | RWC | PID Controller Output Underflow<br>Write 1 to Clear The PID Saturation Flag | 0x0 |

| AFE_ | AFE_STATUS: (Address 0Ch) AFE Status Register |     |                                                                    |         |  |  |  |

|------|-----------------------------------------------|-----|--------------------------------------------------------------------|---------|--|--|--|

| Bit  | Symbol                                        | R/W | Description                                                        | Default |  |  |  |

| 7    | AFE_BUSY                                      | RO  | AFE Work Busy                                                      | 0x0     |  |  |  |

| 6    | RESERVED                                      | RO  | Reserved                                                           | 0x0     |  |  |  |

| 5    | HALL_DIV_DIV0                                 | RWC | HALL_DIV Divide Zero Flag Write 1 to Clear the Feedback Error Flag | 0x0     |  |  |  |

| 4    | AFE_ERR                                       | RWC | AFE Error Flag Write 1 to Clear the Feedback Error Flag            | 0x0     |  |  |  |

| 3    | AFE_TIME_OUT                                  | RO  | AFE Timeout Flag                                                   | 0x0     |  |  |  |

| 2:0  | ADC_CUR_CH                                    | RO  | ADC Current Digital Channel                                        | 0x0     |  |  |  |

| ADC_CH0H: (Address 0Dh) ADC Channel 0 Data High Part |          |     |                              |         |  |

|------------------------------------------------------|----------|-----|------------------------------|---------|--|

| Bit                                                  | Symbol   | R/W | Description                  | Default |  |

| 7:0                                                  | ADC_CH0H | RO  | ADC Channel 0 Data High Part | 0x00    |  |

| ADC | ADC_CH0L: (Address 0Eh) ADC Channel 0 Data Low Part |     |                             |         |  |  |

|-----|-----------------------------------------------------|-----|-----------------------------|---------|--|--|

| Bit | Symbol                                              | R/W | Description                 | Default |  |  |

| 7:0 | ADC_CH0L                                            | RO  | ADC Channel 0 Data Low Part | 0x00    |  |  |

| ADC | ADC_CH1H: (Address 0Fh) ADC Channel 1 Data High Part |     |                              |             |         |

|-----|------------------------------------------------------|-----|------------------------------|-------------|---------|

| Bit | Symbol                                               | R/W |                              | Description | Default |

| 7:0 | ADC_CH1H                                             | RO  | ADC Channel 1 Data High Part |             | 0x00    |

|     |                                                      |     |                              |             |         |

| ADC | ADC_CH1L: (Address 10h) ADC Channel 1 Data Low Part |     |                             |         |  |

|-----|-----------------------------------------------------|-----|-----------------------------|---------|--|

| Bit | Symbol                                              | R/W | Description                 | Default |  |

| 7:0 | ADC_CH1L                                            | RO  | ADC Channel 1 Data Low Part | 0x00    |  |

| ADC | ADC_CH2H: (Address 11h) ADC Channel 2 Data High Part |     |                              |         |  |

|-----|------------------------------------------------------|-----|------------------------------|---------|--|

| Bit | Symbol                                               | R/W | Description                  | Default |  |

| 7:0 | ADC_CH2H                                             | RO  | ADC Channel 2 Data High Part | 0x00    |  |

|     |                                                      |     |                              |         |  |

| ADC_CH2L: (Address 12h) ADC Channel 2 Data Low Part |          |     |                             |             |         |

|-----------------------------------------------------|----------|-----|-----------------------------|-------------|---------|

| Bit                                                 | Symbol   | R/W |                             | Description | Default |

| 7:0                                                 | ADC_CH2L | RO  | ADC Channel 2 Data Low Part |             | 0x00    |

| EIS_ | EIS_OUTH: (Address 13h) EIS Output Data High Part |     |                           |         |  |  |

|------|---------------------------------------------------|-----|---------------------------|---------|--|--|

| Bit  | Symbol                                            | R/W | Description               | Default |  |  |

| 7:0  | EIS_OUTH                                          | RO  | EIS Output Data High Part | 0x10    |  |  |

| EIS_ | EIS_OUTL: (Address 14h) EIS Output Data Low Part |     |                          |         |  |  |

|------|--------------------------------------------------|-----|--------------------------|---------|--|--|

| Bit  | Symbol                                           | R/W | Description              | Default |  |  |

| 7:0  | EIS_OUTL                                         | RO  | EIS Output Data Low Part | 0x00    |  |  |

| DRV | DRV_OUTH: (Address 15h) Driver Output Data High Part |     |                              |         |  |

|-----|------------------------------------------------------|-----|------------------------------|---------|--|

| Bit | Symbol                                               | R/W | Description                  | Default |  |

| 7:0 | DRV_OUTH                                             | RO  | Driver Output Data High Part | 0x08    |  |

| DRV | DRV_OUTL: (Address 16h) Driver Output Data Low Part |     |                             |         |  |  |  |

|-----|-----------------------------------------------------|-----|-----------------------------|---------|--|--|--|

| Bit | Symbol                                              | R/W | Description                 | Default |  |  |  |

| 7:0 | DRV_OUTL                                            | RO  | Driver Output Data Low Part | 0x00    |  |  |  |

| SCS | R: (Address 1Eh) Servo Cor | vergence | Status Register                                                                                         |         |

|-----|----------------------------|----------|---------------------------------------------------------------------------------------------------------|---------|

| Bit | Symbol                     | R/W      | Description                                                                                             | Default |

| 7   | AUTO_SCSW_EN               | RW       | Auto-Switch Scenes Parameter Enable 0: Disable 1: Enable                                                | 0x0     |

| 6   | DIRECT_JUMP                | RO       | Indicate Jump to Direct When 1                                                                          | 0x0     |

| 5   | SCSW2FLS_BUSY              | RO       | Indicate That Scenes is Switching                                                                       | 0x0     |

| 4   | SCSW2FLS_HIS               | RO       | Indicate the historical operation of Scene Switching                                                    | 0x0     |

| 3   | SCSW2FLS_CUR               | RO       | Indicate That Scenes Switch Has Happened for Current Target Access SCSR to Clear the SCSW2FLS_CUR Flag. | 0x0     |

| 2   | VIBRATING                  | RO       | Close Loop Vibrating                                                                                    | 0x0     |

| 1   | CONVERGED                  | RO       | Close Loop Converged                                                                                    | 0x0     |

| 0   | REVIBRATE                  | RO       | Close Loop Re-vibrating Access SCSR to Clear the REVIBRATE Flag.                                        | 0x0     |

| SCS | SCSTCNTH: (Address 1Fh) Servo Convergence Settling Time |     |                                                       |         |  |

|-----|---------------------------------------------------------|-----|-------------------------------------------------------|---------|--|

| Bit | Symbol                                                  | R/W | Description                                           | Default |  |

| 7:0 | SCSTCNTH                                                | RO  | Servo Convergence Time Time = { SCSTCNTH, SCSTCNTL }; | 0x00    |  |

| SCS | SCSTCNTL: (Address 20h) Servo Convergence Settling Time |     |                                                                |         |  |  |

|-----|---------------------------------------------------------|-----|----------------------------------------------------------------|---------|--|--|

| Bit | Symbol                                                  | R/W | Description                                                    | Default |  |  |

| 7:0 | SCSTCNTL                                                | RO  | Servo Convergence Settling Time Time = { SCSTCNTH, SCSTCNTL }; | 0x00    |  |  |

| Bit | Symbol            | R/W | Description                                   | Default |

|-----|-------------------|-----|-----------------------------------------------|---------|

| 7:5 | SCSW_AUTO_JUMPDIR | RO  | Scenes Switch Auto Jump Direction             | 0x0     |

| 4:2 | ERGD_JUMPDIR      | RO  | Ergodic Operation Jump Direction              | 0x0     |

| 1   | ERGD_DONE         | RO  | Ergodic Operation Done                        | 0x0     |

| 0   | ERGD_BYPASS       | RW  | Ergodic Operation Enable 0: Disable 1: Enable | 0x1     |

| Bit | Symbol | R/W | Description                                                                                                                                                                                            | Default |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:0 | SCSWCR | RW  | Scenes Switch Controller Register Must Enable FLS_KEY before Access SCSWCR 0x1A: 1th Scene, Read Out 0x01 0x2A: 2th Scene, Read Out 0x02 0x3A: 3th Scene, Read Out 0x03 0x4A: 4th Scene, Read Out 0x04 | 0x00    |

| ACC_FLS_KEY: (Address 23h) Access eFlash Key |         |     |                                                                                            |         |

|----------------------------------------------|---------|-----|--------------------------------------------------------------------------------------------|---------|

| Bit                                          | Symbol  | R/W | Description                                                                                | Default |

| 7:0                                          | FLS_KEY | RW  | Access EFLASH Key Write 0x8A to enable eFlash access authority, Read 0x01 when be enabled. | 0x00    |

| ACC_CAC_KEY: (Address 24h) Access CACHE Key |         |     |                                                                                          |         |  |

|---------------------------------------------|---------|-----|------------------------------------------------------------------------------------------|---------|--|

| Bit                                         | Symbol  | R/W | Description                                                                              | Default |  |

| 7:0                                         | CAC_KEY | RW  | Access CACHE Key Write 0x5A to enable CACHE access authority, Read 0x01 when be enabled. | 0x00    |  |

| WP_ | WP_UNLOCK: (Address 26h) Write Protection Unlock Key |     |                                                                                                                                                                                                                     |         |  |

|-----|------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit | Symbol                                               | R/W | Description                                                                                                                                                                                                         | Default |  |

| 7:0 | WP_UNLOCK                                            | RW  | Write Protection Unlock Key Write 0x88 to unlock Chip Erase protection, Read 0x04 when be enabled. Write 0x55 to unlock eFlash Main Program & Erase protection, Read 0x01 when be enabled. (For head 500bytes only) | 0x00    |  |

| Bit | Symbol | R/W | Description                                                                                                                                                                                                           | Default |

|-----|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:0 | ОСРО   | RW  | One Click Program When Write: 0x87: Main One Click Program Trigger. When Read: Bit[7:6]: Reserved Bit[5]: NVR OCP Flag, auto clear when OCP done. Bit[4]: NVR OCP Flag, auto clear when OCP done. Bit[3:0]: OCP_STATE | 0x00    |

| EFLA | ASH_ADDR0: (Address 28h) E | Bridge eFla | ash Access Address High Part                                                                                                                                           |         |

|------|----------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit  | Symbol                     | R/W         | Description                                                                                                                                                            | Default |

| 7    | BDGFLSNVR                  | RW          | Bridge eFlash Access NVR Enable<br>Must Enable FLS_KEY before Access BDGFLSNVR                                                                                         | 0x0     |

| 6:4  | RESERVED                   | RW          | Reserved                                                                                                                                                               | 0x0     |

| 3:0  | BDGFLSADDR0                | RW          | Bridge eFlash Access Address High Part Must Enable FLS_KEY before Access BDGFLSADDR0. Unit is Byte, But Must Align By Word. Address = (BDGFLSADDR0 << 8) + BDGFLSADDR1 | 0x0     |

| EFLA | EFLASH_ADDR1: (Address 29h) Bridge eFlash Access Address Low Part |     |                                                                                                                                                                         |         |  |  |

|------|-------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit  | Symbol                                                            | R/W | Description                                                                                                                                                             | Default |  |  |

| 7:0  | BDGFLSADDR1                                                       | RW  | Bridge eFlash Access Address Low Part Must Enable FLS_KEY before Access BDGFLSADDR1. Unit is Byte, But Must Align By Word. Address = ( BDGFLSADDR0 << 8 ) + BDGFLSADDR1 | 0x00    |  |  |

| EFLA | EFLASH_MAP0: (Address 2Ah) ISP eFlash Mapping Address High Part |     |                                                                                                                                                                        |         |  |

|------|-----------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit  | Symbol                                                          | R/W | Description                                                                                                                                                            | Default |  |

| 7:0  | ISPFLSMAP0                                                      | RW  | ISP eFlash Mapping Address High Part Must Enable FLS_KEY before Access ISPFLSMAP0. Unit Is Byte, But Must Be Align By Word. Address = ( ISPFLSMAP0 << 8 ) + ISPFLSMAP1 | 0x00    |  |

| EFL | EFLASH_MAP1: (Address 2Bh) ISP eFlash Mapping Address Low Part |     |                                                                                                                                                                       |         |  |  |

|-----|----------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit | Symbol                                                         | R/W | Description                                                                                                                                                           | Default |  |  |

| 7:0 | ISPFLSMAP1                                                     | RW  | ISP eFlash Mapping Address Low Part Must Enable FLS_KEY before Access ISPFLSMAP1. Unit Is Byte, But Must Be Align By Word. Address = ( ISPFLSMAP0 << 8 ) + ISPFLSMAP1 | 0x00    |  |  |

| CAC | CACHE_MAP: (Address 2Ch) CACHE Mapping Address |     |                                                                                                          |         |  |  |

|-----|------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit | Symbol                                         | R/W | Description                                                                                              | Default |  |  |

| 7:0 | CACMAP                                         | RW  | CACHE Mapping Address Must Enable FLS_KEY before Access CACMAP. Unit Is Byte, But Must Be Align By Word. | 0x00    |  |  |

| CI | CMD_WORD_LEN: (Address 2Dh) ISP Access Byte Length |        |     |                                                                                                          |         |  |

|----|----------------------------------------------------|--------|-----|----------------------------------------------------------------------------------------------------------|---------|--|

| Bi | it                                                 | Symbol | R/W | Description                                                                                              | Default |  |

| 7: | 0                                                  | ISPWL  | RW  | ISP Access Word Length Must Enable FLS_KEY before Access ISPWL. Unit Is Byte, But Must Be Align By Word. | 0x3F    |  |

| Bit | ASH_CFG: (Address 2Eh) 6  Symbol | eFlash Co | Description                                                                                                                                                                                       | Default |

|-----|----------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | ISP_TESTEN                       | RW        | eFlash Test Enable Must Enable FLS_KEY before Access ISP_TESTEN 0: disable 1: enable                                                                                                              | 0x0     |

| 6   | ISP_DPSTB_EN                     | RW        | Deep Standby Enable Must Enable FLS_KEY before Access ISP_DPSTB_EN 0: disable 1: enable                                                                                                           | 0x1     |

| 5   | ISP_MAIN_EN                      | RW        | eFlash Main Memory Access Enable Must Enable FLS_KEY before Access ISP_MAIN_EN 0: disable 1: enable                                                                                               | 0x1     |

| 4   | ISP_NVR_EN                       | RW        | eFlash NVR Memory Access Enable Must Enable FLS_KEY before Access ISP_NVR_EN 0: disable 1: enable                                                                                                 | 0x0     |

| 3   | ISP_BLOCK                        | RW        | ISP Block Access Enable Must Enable FLS_KEY before Access ISP_BLOCK. Configure When Block Erase. Every Block Contains 128Bytes, ISPFLSMAP0[11:7] Indicate Which Block.                            | 0x0     |

| 2   | ISP_NVR                          | RW        | ISP NVR Main Memory Selector Must Enable FLS_KEY before Access ISP_NVR 0: Main Array 1: NVR Every NVR Contains 64Bytes; NVR2 Program By Fab, ISPFLSMAP1[6] Indicate NVR1 or NVR2. 0: NVR1 1: NVR2 | 0x0     |

| 1   | ISP_CHIP                         | RW        | ISP Chip Access Enable Must Enable FLS_KEY before Access ISP_CHIP. Configure When Chip Erase. 0: disable 1: enable                                                                                | 0x0     |

| 0   | ISP_EN                           | RW        | ISP Access Enable Must Enable FLS_KEY before Access ISP_EN 0: eFlash Bridge 1: ISP                                                                                                                | 0x0     |

| CMD | : (Address 2Fh) ISP Access C | ontroller |                                                                                                                                                                                                                                       |         |

|-----|------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit | Symbol                       | R/W       | Description                                                                                                                                                                                                                           | Default |

| 7:4 | RESERVED                     | RW        | Reserved                                                                                                                                                                                                                              | 0x0     |

| 3:0 | ISP_CMD                      | RW        | ISP Access Command Write 0x00 to eFlash data Load And Refresh Data To Cache. Write 0x02 to Program And Save Data From Cache. Write 0x04 to Erase. Write 0x08 to Load NVR1/MAIN And Refresh To Cache. Write 0x0A to Load Only for CRC. | 0x8     |

| CMD | CMD_GO: (Address 30h) ISP Access Go Trigger |     |                                                                      |         |  |

|-----|---------------------------------------------|-----|----------------------------------------------------------------------|---------|--|

| Bit | Symbol                                      | R/W | Description                                                          | Default |  |

| 7:0 | ISP_GO                                      | RW  | ISP Access Go Trigger<br>Write 0xAA to Enable ISP Access Go Trigger. | 0x00    |  |