# Nine-Channel LED Driver with Execution ENGINE and Charge Pump

#### **Features**

awinic

- Power Supply Voltage Range: 2.7V to 5.5V

- Operating Temperature Range: -40°C to 105°C

- 9 Independent Programmable LED Channels

- Each Channel Supports an 8-Bit Current Setting, with a Maximum Output Current of 25.5mA

- Each Channel Features 12-Bit PWM Control Resolution

- High-efficiency Adaptive Charge Pump (1x/1.5x)

with Efficiency up to 94%

- Charge Pump Incorporates Soft Start,

Overcurrent, and Short-Circuit Protection

- LED Driver Efficiency Reaches up to 93%

- Integrated Open-Circuit, Short-Circuit, and Voltage Error Detection

- Automatic Power-Saving Mode

- Three Independent Program Execution Engines

- Large SRAM Program Memory

- I<sup>2</sup>C interface

- Supports Cascading Applications

- Low-level external trigger function

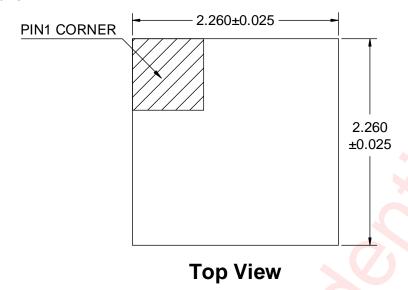

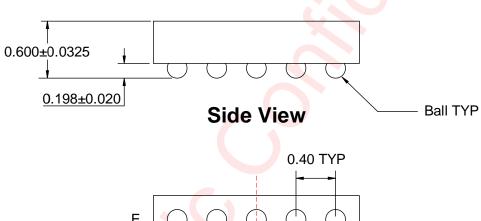

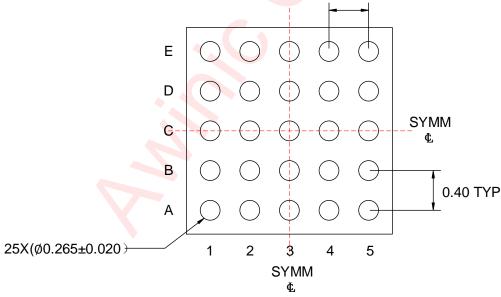

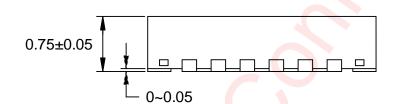

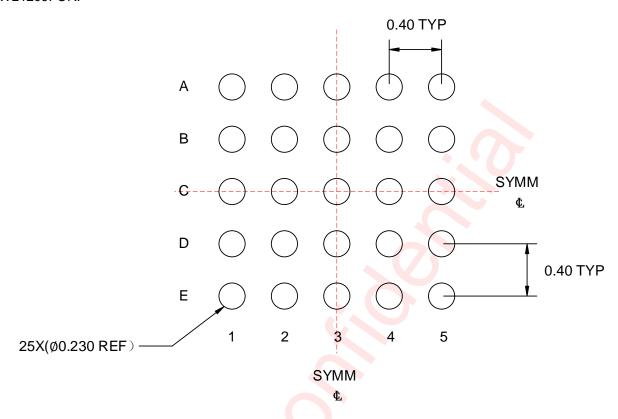

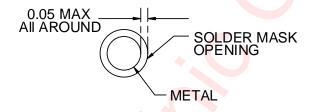

- AW21209FOR package: FOWLP 2.26X2.26-25B

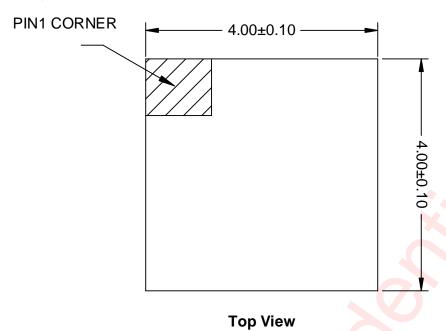

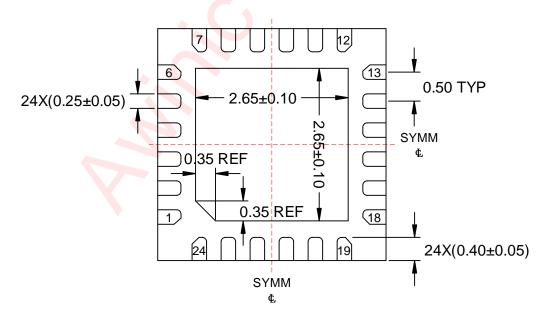

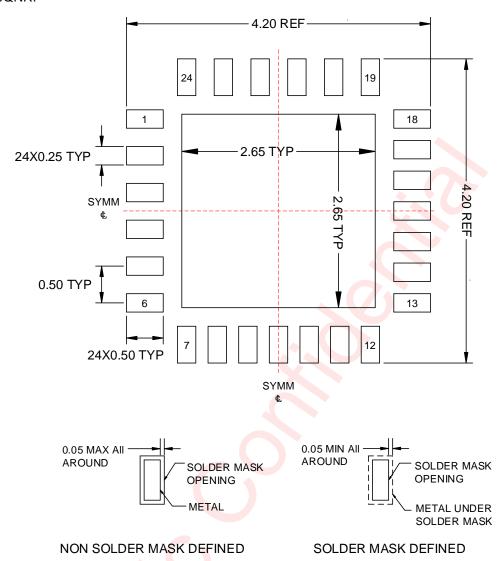

- AW21209QNR package: QFN 4X4-24L

## **Applications**

- Ambient light

- Indicator light

- Electronic cigarette

- Bluetooth headphones

- Speaker

- Programmable current source

- VR/XR/AR

### **General Description**

AW21209 is a programmable 9-channel LED driver specifically designed for mobile devices. It features an internal program memory that enables it to operate independently without the need for an external processor and generate the desired lighting effects. There are two products in total: AW21209FOR and AW21209QNR. Since the AW21209QNR has no GPO pins, all control logic related to GPO (such as the GPO bit in the IO\_CTRL register and the mapping function of GPO in the LED mapping instruction) is not applicable.

AW21209 is equipped with an efficient charge pump that can drive LEDs across the entire voltage range of lithium-ion batteries and automatically selects the optimal charge pump gain to meet the forward voltage requirements of the LEDs, ensuring high efficiency over a wide operating voltage range. When the LEDs are not activated, the AW21209 automatically enters a power-saving mode, significantly reducing current consumption in idle states.

AW21209 features a control interface compatible with the I<sup>2</sup>C protocol and supports four different address selections, facilitating system integration. The TRIG pin can trigger the operation of light effects and synchronize multiple devices. The INT pin can send an interrupt signal to the processor after the lighting sequence is completed. The GPO pin can be used as a digital control pin for other devices.

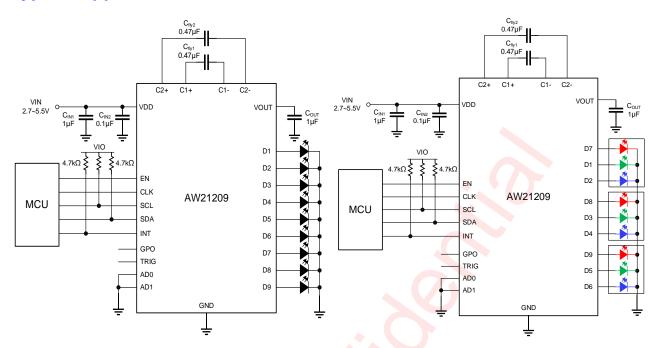

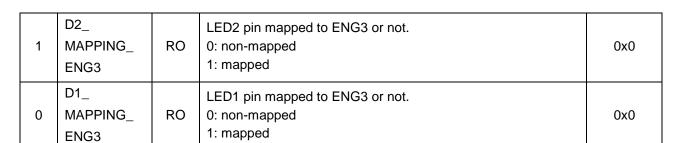

## **Typical Application Circuit**

Figure 1 AW21209 Simple Application Circuit

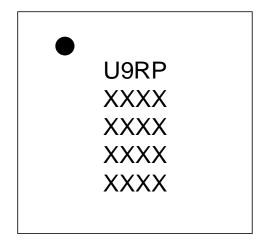

## **Pin Configuration And Top Mark**

AW21209FOR (Top View)

1 2 3 4 5

VOUT) Α В (D4) (AD1) (C1-) C (EN) (VDD) (D6) (ADO) (D7) (D8) (INT) (CLK) D (GND) Ε (D9) (GPO) TRIG) (SDA) (SCL)

AW21209FOR Marking (Top View)

U9RP - AW21209FOR XXXX/XXXX/XXXX/XXXX -Production Tracing Code

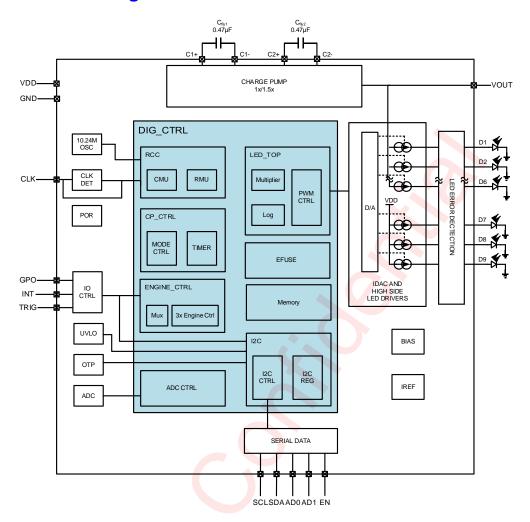

# AW21209QNR (Top View)

# AW21209QNR Marking (Top View)

Z04R - AW21209QNR XXXX - Production Tracing Code

Figure 2 Pin Configuration and Marking

### **Pin Definition**

| No.<br>AW21209FOR | No.<br>AW21209QNR | NAME | DESCRIPTION                                                                                                |

|-------------------|-------------------|------|------------------------------------------------------------------------------------------------------------|

| A1                | 19                | D1   | Constant current source, connect to LED's anode.                                                           |

| A2                | 18                | D2   | Constant current source, connect to LED's anode.                                                           |

| A3                | 22                | VOUT | Charge pump output voltage, connect to a 1µF capacitor.                                                    |

| A4                | 23                | C2-  | Switched cap flying cap connection. Connect a 0.47µF capacitor between this pin and C2+.                   |

| A5                | 1                 | C2+  | Switched cap flying cap connection. Connect a 0.47µF capacitor between this pin and C2                     |

| B1                | 17                | D3   | Constant current source, connect to LED's anode.                                                           |

| B2                | 16                | D4   | Constant current source, connect to LED's anode.                                                           |

| В3                | 21                | AD1  | I <sup>2</sup> C address setting, connects to GND or VDD for different device address of I <sup>2</sup> C. |

| B4                | 24                | C1-  | Switched cap flying cap connection. Connect a 0.47µF capacitor between this pin and C1+.                   |

| B5                | 2                 | C1+  | Switched cap flying cap connection. Connect a 0.47µF capacitor between this pin and C1                     |

| C1                | 15                | D5   | Constant current source, connect to LED's anode.                                                           |

| C2                | 14                | D6   | Constant current source, connect to LED's anode.                                                           |

| C3                | 20                | AD0  | I <sup>2</sup> C address setting, connects to GND or VDD for different device address of I <sup>2</sup> C. |

| C4 | 5  | EN          | Shutdown the chip when pulled low.                      |  |

|----|----|-------------|---------------------------------------------------------|--|

| C5 | 3  | VDD         | Power supply: 2.7V~5.5V.                                |  |

| D1 | 13 | D7          | Constant current source, connect to LED's anode.        |  |

| D2 | 12 | D8          | Constant current source, connect to LED's anode.        |  |

| D3 | 7  | INT         | Interrupt, low active, leave unconnected if not used.   |  |

| D4 | 6  | CLK         | External 32kHz clock input, connect to GND if not used. |  |

| D5 | 4  | GND         | Ground.                                                 |  |

| E1 | 11 | D9          | Constant current source, connect to LED's anode.        |  |

| E2 | -  | GPO         | General purpose output, leave unconnected if not used.  |  |

| E3 | 10 | TRIG        | Trigger, connect to GND if not used.                    |  |

| E4 | 8  | SDA         | Serial data I/O for I <sup>2</sup> C interface.         |  |

| E5 | 9  | SCL         | Serial clock input for I <sup>2</sup> C interface.      |  |

| -  | 25 | Thermal pad | Only for heat dissipation                               |  |

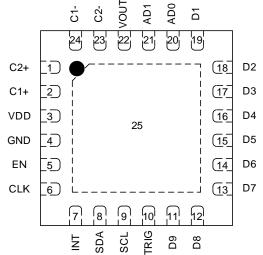

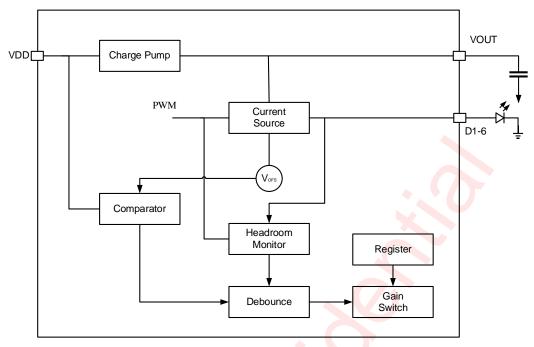

## **Functional Block Diagram**

Figure 3 Functional Block Diagram

## **Ordering Information**

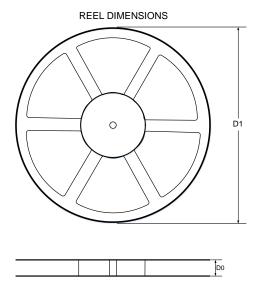

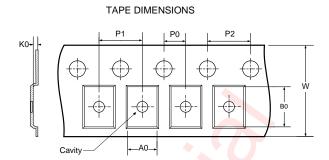

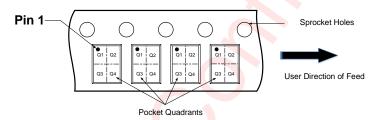

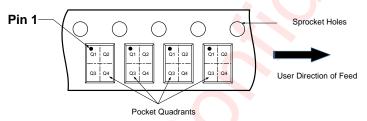

| Part Number | Temperature | Package                 | Marking | Moisture<br>Sensitivity Level | Environmental Information | Delivery Form                |

|-------------|-------------|-------------------------|---------|-------------------------------|---------------------------|------------------------------|

| AW21209FOR  | -40°C∼105°C | FOWLP 2.26X2.26-<br>25B | U9RP    | MSL1                          | ROHS+HF                   | 3000 units/<br>Tape and Reel |

| AW21209QNR  | -40°C∼105°C | QFN 4X4-24L             | Z04R    | MSL1                          | ROHS+HF                   | 4500 units/<br>Tape and Reel |

Aug. 2025 V1.3

## **Absolute Maximum Ratings**(NOTE1)

|                     | PARAMETERS                                                              |                |  |  |  |

|---------------------|-------------------------------------------------------------------------|----------------|--|--|--|

| Sup                 | ply voltage range VDD                                                   | -0.3V to 6V    |  |  |  |

| Input voltage range | D1 to D9, C1-,C1+,C2-,C2+,VOUT,<br>EN,CLK,INT,SDA,SCL,TRIG,ASEL0,ASEL1, | -0.3V to VDD   |  |  |  |

| Junction-to-ambient | thermal resistance θ <sub>JA</sub> (AW21209FOR)                         | 78.9°C/W       |  |  |  |

| Junction-to-ambient | thermal resistance θ <sub>JA</sub> (AW21209QNR)                         | 50°C/W         |  |  |  |

| Maximum ope         | Maximum operating junction temperature T <sub>JMAX</sub>                |                |  |  |  |

| Stora               | age temperature T <sub>STG</sub>                                        | -65°C to 150°C |  |  |  |

| Lead tempe          | erature (soldering 10 seconds)                                          | 260°C          |  |  |  |

|                     | ESD (Including CDM HBM)(NOTE 2)                                         |                |  |  |  |

|                     | НВМ                                                                     | ±4kV           |  |  |  |

|                     | CDM                                                                     |                |  |  |  |

|                     | Latch-Up                                                                |                |  |  |  |

| Tes                 | Test condition: JESD78F                                                 |                |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. HBM test method: ESDA/JEDEC JS-001-2023(AW21209FOR), ESDA/JEDEC JS-001-2024(AW21209QNR), CDM test method: ESDA/JEDEC JS -002-2022

## **RECOMMENDED OPERATING CONDITIONS**

| Symbol            | Parameter                                    | Min.     | Тур. | Max. | Unit |

|-------------------|----------------------------------------------|----------|------|------|------|

| VDD               | Input voltage                                | 2.7      | 3.6  | 5.5  | V    |

| VDD               | Voltage on logic pins (input or output pins) | 0        |      | VDD  | V    |

| l <sub>out</sub>  | Recommended charge pump load current         |          |      | 150  | mA   |

| TA                | Operating free-air temperature range         | -40°     | 25   | 105  | °C   |

| C <sub>IN1</sub>  | Input Capacitance                            | 0.5      | 1    |      | μF   |

| C <sub>IN2</sub>  | Input Capacitance                            | <b>\</b> | 0.1  |      | μF   |

| Соит              | Output Capacitance                           | 0.5      | 1    | 4.7  | μF   |

| C <sub>fly1</sub> | Charge pump capacitance                      | 0.24     | 0.47 | 1    | μF   |

| C <sub>fly2</sub> | Charge pump capacitance                      | 0.24     | 0.47 | 1    | μF   |

## **Electrical Characteristics**

Typical values apply for T<sub>A</sub>=25°C, V<sub>DD</sub>=3.6V ,V<sub>EN</sub>=1.2V, C<sub>out</sub>=1 $\mu$ F, C<sub>IN</sub>=0.1 $\mu$ F, C<sub>fly1</sub>= C<sub>fly2</sub>=0.47 $\mu$ F.

|                       | PARAMETER                              | TEST CONDITION                                                                | MIN | TYP  | MAX | UNIT |

|-----------------------|----------------------------------------|-------------------------------------------------------------------------------|-----|------|-----|------|

| Power su              | apply voltage and current              |                                                                               |     |      |     |      |

|                       |                                        | EN=L,CHIP_EN=0(bit),external<br>32-Khz clock running or not<br>running        |     | 0.2  | 1   | μA   |

|                       | Standby supply current                 | EN=H, CHIP_EN=0, external 32KHZ clock not running                             | . ( | 1    | 2   | μА   |

|                       |                                        | EN=H, CHIP_EN=0, external 32KHZ clock running                                 |     | 1.4  | 3   | μΑ   |

| I <sub>VDD</sub>      |                                        | External 32KHz clock running, charge pump and current source outputs disabled |     | 0.33 | 0.5 | mA   |

|                       | Normal mode supply current             | Charge pump in 1X mode, no load current source outputs disabled               |     | 0.55 | 0.8 | mA   |

|                       |                                        | Charge pump in 1.5X mode, no load, current source outputs disabled            |     | 1.8  | 2   | mA   |

|                       | Power save mode                        | External 32Khz clock running                                                  |     | 5    | 10  | μA   |

|                       | supply current                         | Internal oscillator running                                                   |     | 0.3  | 0.5 | mA   |

| f <sub>osc</sub>      | Internal oscillator frequency accuracy |                                                                               | -4% |      | 4%  |      |

| OTP                   | Over temperature protection threshold  |                                                                               |     | 150  |     | °C   |

| OTP <sub>HYS</sub>    | Over temperature protection hysteresis |                                                                               |     | 20   |     | °C   |

| Charge P              | ump                                    |                                                                               |     |      |     |      |

| R <sub>out</sub>      | Charge pump output                     | Gain=1.5X                                                                     |     | 3.5  |     | Ω    |

| Nout                  | resistance                             | Gain=1X                                                                       |     | 1    |     | 22   |

| T <sub>ON</sub>       | Vout turn-on time                      | VDD=3.6V, lout=60mA                                                           |     |      | 120 | μs   |

| LED Driv              | er                                     |                                                                               |     | 1    |     | •    |

| I <sub>Leakage</sub>  | Leakage current<br>(outputs D1 to D9)  | PWM =0%                                                                       |     | 0.1  | 1   | μA   |

| I <sub>MAX</sub>      | Maximum source current                 | Outputs D1 to D9                                                              |     | 25.5 |     | mA   |

| I <sub>accuracy</sub> | Output current accuracy                | Output current set to 17.5mA                                                  | -4  |      | 4   | %    |

| Іматсн                | Matching                               | Output current set to 17.5mA                                                  |     | 1    | 2.5 | %    |

| f <sub>led</sub>      | LED switching frequency                |                                                                               |     | 312  |     | Hz   |

| Vsat                  | Saturation voltage                     | Output current set to 17.5mA                                                  |     | 50   | 100 | mV   |

| ADC                   |                                        |                                                                               |     |      |     |      |

| LSB                   | Least significant bit                  |                                                                               |     | 28.6 |     | mV   |

| E <sub>ABS</sub>      | Total unadjusted error                 | V <sub>IN_TEST</sub> =0V to VDD                                               |     | <±3  |     | LSB  |

| PARAMETER            |                         | TEST CONDITION                        | MIN                     | TYP         | MAX                     | UNIT |  |

|----------------------|-------------------------|---------------------------------------|-------------------------|-------------|-------------------------|------|--|

| t <sub>conv</sub>    | Conversion time         |                                       |                         | 2.7         |                         | ms   |  |

| V <sub>IN_TEST</sub> | DC voltage sample range |                                       | 0                       |             | 5                       | V    |  |

| LOGIC IN             | IPUT EN                 |                                       |                         |             |                         |      |  |

| $V_{IL}$             | Input low level         |                                       |                         |             | 0.24                    | V    |  |

| ViH                  | Input high level        |                                       | 0.96                    |             |                         | V    |  |

| I <sub>L</sub>       | Input current           |                                       | -1                      |             | 1                       | μA   |  |

| T <sub>DELAY</sub>   | Input delay             |                                       |                         | 2           |                         | μs   |  |

| LOGIC IL             | JTPUT SDA, TRIG, INT    |                                       | <b>*</b>                |             |                         |      |  |

| VıL                  | Input low level         |                                       |                         |             | 0.2*<br>V <sub>EN</sub> | V    |  |

| VIH                  | Input high level        |                                       | 0.8*<br>V <sub>EN</sub> |             |                         | V    |  |

| I <sub>L</sub>       | Input current           | . (/                                  | -1                      |             | 1                       | μA   |  |

| LOGIC O              | UTPUT SDA, TRIG, INT    |                                       |                         |             |                         |      |  |

| VoL                  | Output low level        | I <sub>ОUT</sub> =3mA(pullup current) |                         | 0.3         |                         | V    |  |

| IL.                  | Output leakage current  | V <sub>OUT</sub> =2.8V                |                         |             | 1                       | μA   |  |

| LOGIC OUTPUT GPO     |                         |                                       |                         |             |                         |      |  |

| VoL                  | Output low level        | Іоит=3mA                              |                         | 0.3         |                         | V    |  |

| Vон                  | Output high level       | I <sub>OUT</sub> =-2mA                |                         | VDD-<br>0.3 |                         |      |  |

| lι                   | Output leakage current  | Vout=2.8V                             |                         |             | 1                       | μA   |  |

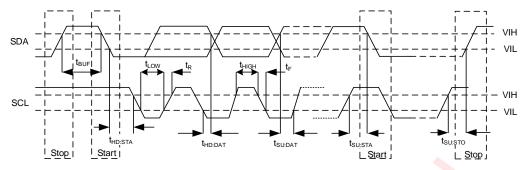

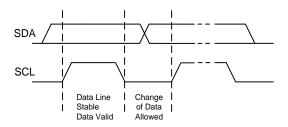

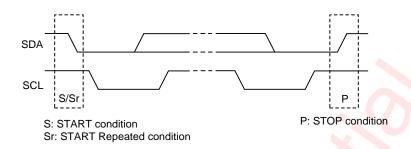

## I<sup>2</sup>C INTERFACE TIMING REQUIREMENTS

|                     | Parameter                                 |      |      | Fast M | Unit |     |

|---------------------|-------------------------------------------|------|------|--------|------|-----|

|                     | Parameter                                 | Min. | Max. | Min.   | Max. |     |

| F <sub>SCL</sub>    | Interface clock frequency                 | -    | 400  | -      | 1000 | kHz |

| T <sub>HD:STA</sub> | (Repeat-start) START condition hold time  | 0.6  | -    | 0.26   | -    | μs  |

| T <sub>LOW</sub>    | Low level width of SCL                    | 1.3  | -    | 0.5    | -    | μs  |

| T <sub>HIGH</sub>   | High level width of SCL                   |      | -    | 0.26   | -    | μs  |

| T <sub>SU:STA</sub> | (Repeat-start) START condition setup time |      | -    | 0.26   | -    | μs  |

| T <sub>HD:DAT</sub> | Data hold time                            | 0    | -    | 0      | -    | μs  |

| T <sub>SU:DAT</sub> | Data setup time                           | 0.1  | -    | 0.05   | -    | μs  |

| T <sub>R</sub>      | Rising time of SDA and SCL                | -    | 0.3  | -      | 0.12 | μs  |

| T <sub>F</sub>      | Falling time of SDA and SCL               | -    | 0.3  | -      | 0.12 | μs  |

| T <sub>SU:STO</sub> | STOP condition setup time                 |      | -    | 0.26   | -    | μs  |

| T <sub>BUF</sub>    | Time between start and stop condition     | 1.3  | -    | 0.5    | -    | μs  |

Figure 4 I<sup>2</sup>C Interface Timing

## **Detailed Functional Description**

#### **Overview**

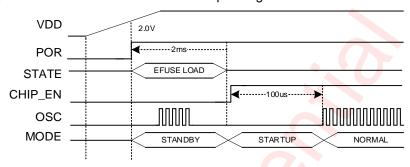

AW21209 is a programmable 9-channel LED driver specifically designed for mobile devices. Device includes charge pump, high-side current sources, I<sup>2</sup>C interface, program execution engines and temperature compensation. Each channel supports an 8-bit current setting, with a maximum output current of 25.5mA, each channel features 12-bit pwm control resolution. Device startup timing is showed below.

Figure 5 startup timing

#### **Dimming**

#### **Analog Dimming**

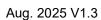

Analog dimming of AW21209 is controlled by individual 8-bit LED CURRENT register setting.

Table 1 DX\_CURRENT Register (26H-2EH)

| 8-BIT CURR | 8-BIT CURRENT register |      |  |

|------------|------------------------|------|--|

| Binary     | Decimal                | mA   |  |

| 0000_0000  | 0                      | 0.0  |  |

| 0000_0001  | 1                      | 0.1  |  |

| 0000_0010  | 2                      | 0.2  |  |

| 0000_0011  | 3                      | 0.3  |  |

|            |                        |      |  |

| 1010_1111  | 175                    | 17.5 |  |

|            |                        |      |  |

| 1111_1110  | 254                    | 25.4 |  |

| 1111_1111  | 255                    | 25.5 |  |

#### 上海文列电子放爪股份有限公司 shanghai awinic technology co., ltd.

#### **PWM Dimming**

AW21209 has 9 LED ports, each of which is controlled by an independent PWM output register (16H - 1EH). When PWM is not FF, duty cycle is (PWM/256)\*100%; When PWM is FF, duty cycle is 100%.

The system clock operates at 10.24 MHz and can be configured with the division factor and PWM mode through the PWM\_CFG register (80H). The specific configuration is as follows:

| PWM_DIV      | 0        | 1       | 2       | 3       | 4        | 5       | 6       | 7        |

|--------------|----------|---------|---------|---------|----------|---------|---------|----------|

| pwmclk       | 10.24MHz | 5.12MHz | 2.56MHz | 1.28MHz | 640KHz   | 320KHz  | 160KHz  | 80KHz    |

| 9bit+3Dither | 20KHz    | 10KHz   | 5KHz    | 2.5KHz  | 1.25KHz  | 625Hz   | 312.5Hz | 156.25Hz |

| 12bit        | 2.5KHZ   | 1.25KHz | 625Hz   | 312.5Hz | 156.25Hz | 78.13Hz | 39.06Hz | 19.53Hz  |

**Table 2 PWM frequency**

#### 1. Master Fader Modulation Function

AW21209 is equipped with master fader control, which allows the user to fade in or fade out multiple LEDs by writing to only one register. This is a useful function to minimize serial-bus traffic between the MCU and the AW21209. Users can choose whether to enable the master fader modulation according to their needs. Once enabled, each LED port has three master fader options to choose from.

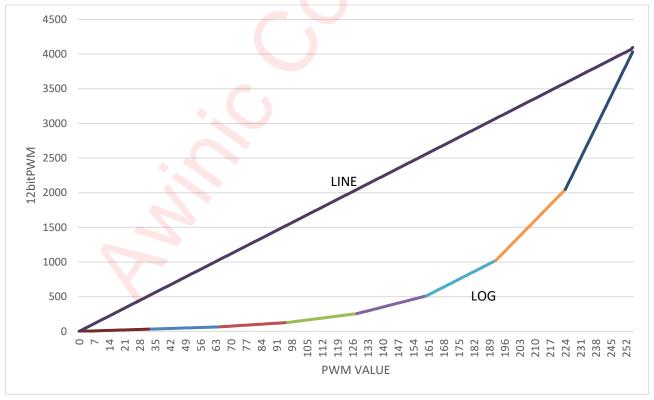

#### 2. Log Compensation Function

Human eyes are more sensitive to dim light. To make the brightness changes more linear to the human eye, device has added a log modulation function. This function can be enabled through the LOG\_EN (06H - 0EH) signal to implement exponential modulation. The implementation is divided into eight segments for precise control.

Figure 6 Linear and Logarithmic dimming curves

#### 3. Temperature Compensation Function

Temperature variations can cause changes in LED brightness and color purity, leading to unexpected color

deviations. To address this, the AW21209 integrates an ADC (Analog-to-Digital Converter) to monitor temperature and regulate the PWM (Pulse Width Modulation) output duty cycle through temperature compensation, thereby achieving light compensation. Additionally, it supports external temperature sensors to capture temperature changes and implement thermal compensation effects. Users can select the slope of the temperature compensation, enabling brightness compensation in different scenarios. The temperature modulation range is from -39°C to 89°C. To provide more margin for better brightness compensation, it is essential to ensure that the PWM output duty cycle does not exceed 50% at 25°C. The compensation calculation formula is as follows:

$$PWM_F = \frac{\left[PWM_S - \left(25 \ \mathcal{C} - T\right) * CorrectionFactor * PWM_S\right]}{2}$$

Among them, PWMs stands for the PWM configuration duty cycle register DX\_PWM, T represents the temperature at the ADC testing point, and Correction Factor represents the temperature compensation slope (which can be freely configured by the ).

Table 3 DX\_TEMP\_COMP Register (06H-0EH)

| Name       | Bits | Description                                        |  |  |

|------------|------|----------------------------------------------------|--|--|

|            |      | Temperature Compensation Slope Selection.          |  |  |

|            |      | Default Temperature: 25°C. Default: Disabled.      |  |  |

|            |      | 0_0000: Disable temperature compensation function; |  |  |

|            |      | 1_1111: enable, 1°C adjust-1.5%;                   |  |  |

|            |      | 1_1110: ena <mark>ble, 1°</mark> C adjust-1.4%;    |  |  |

| TEM_COMP   | 4:0  |                                                    |  |  |

| TENI_GONII | 4.0  | 1_0001: enable, 1°C adjust-0.1%;                   |  |  |

|            |      | 1_0000: enable, 1°C adjust 0%;                     |  |  |

|            |      | 0_0001: enable, 1°C adjust0.1%;                    |  |  |

|            |      |                                                    |  |  |

|            |      | 0_1110: enable∍ 1°C adjust1.4%;                    |  |  |

|            |      | 0_1111: enable, 1°C adjust1.5%;                    |  |  |

#### 4. Data Flow

Each channel supports three types of modulation: master fader, exponential compensation, and temperature compensation. These three modulation modes can be freely combined as needed. For details on the three modulation enable switch configurations, please refer to the table below.

Table 4 Modulation compensation implementation

| LOG_EN | FADER_EN | TEMP_EN | OUTPUT                 |

|--------|----------|---------|------------------------|

| 0      | 0        | 0       | pwm_value              |

| 1      | 0        | 0       | Log(pwm_value)         |

| 0      | 1        | 0       | Master_fader*pwm_value |

| 1 | 1 | 0 | Log(master_fader)*pwm_value       |

|---|---|---|-----------------------------------|

| 0 | 0 | 1 | Temp(pwm_value)                   |

| 1 | 0 | 1 | Temp(Log(pwm_value))              |

| 0 | 1 | 1 | Temp(master_fader*pwm_value)      |

| 1 | 1 | 1 | Temp(Log(master_fader)*pwm_value) |

#### Note:

- 1. pwm\_value is DX\_PWM register configuration value;

- 2. log(pwm\_value) represents the value after applying logarithmic compensation to pwm\_value;

- 3. temp(pwm\_value) represents the value after applying temperature compensation to pwm\_value;

- 4. master\_fader \* pwm\_value refers to the modulation of pwm\_value by master\_fader, where the product retains the high 12 bits.

#### Clock

The clock is a core component for the normal operation of the chip. This chip provides two clock sources: a 10.24MHz high-speed clock and a 32kHz low-speed clock, which meet the requirements of different functional modules.

#### High-speed Clock

The 10.24MHz high-speed clock is generated by the internal oscillator (OSC) and provides a stable clock signal for the LED control module and the charge pump. After normal power-on, the internal OSC will automatically start and generate the 10.24MHz clock to ensure the normal operation of the chip's core functional modules. When the chip enters Power Save mode and the user configures the use of the external clock, the 10.24MHz clock will stop working to further reduce power consumption. It is important to note that when using the external clock and entering Power Save mode, the external clock must remain active; otherwise, the chip will not be able to wake up normally from Power Save mode.

#### Low-speed Clock

The low-speed clock is used for the instruction execution engine, which fetches and executes instructions stored in the internal SRAM to generate the desired lighting effects. The chip defaults to using the external clock on the CLK pin. Users can switch between the external clock and the internally derived 32.768kHz clock by configuring the CLK SEL register.

After power-on and enabling the CHIP\_EN bit in the CONFIG register, the chip requires a minimum of 32µs to detect the external clock. The AW21209 can detect external clock signals with frequencies above 5kHz.If the external clock stops or its frequency drops below 5kHz, the chip will determine that the external clock is invalid. Switching between the internal and external clocks requires a delay of at least 153µs for the change to take effect. To maximize power savings in Power Save mode, users are recommended to configure the chip to use the external clock. When the chip is in Power Save mode and using the external clock, the 10.24MHz clock will be disabled. It is crucial that the external clock remains active during Power Save mode to ensure proper wake-up functionality. Failure to maintain the external clock during Power Save mode may result in the chip being unable to wake up correctly.

**Note:** The EXEC register, MODE register, PWM register, PC register and MASTER\_FADER register are synchronized to the clock. Therefore, they do not support the I<sup>2</sup>C bus's auto-increment write operation. After configuring these registers via the I<sup>2</sup>C bus, a delay of four clock cycles is required for the settings to take effect. This delay ensures proper synchronization with the clock and guarantees stable operation of the chip. When

上海艾为电子技术股份有眼公司 shanghai awinic technology co., ltd.

using an external clock for AW21209, if no clock is provided to the CLK pin before the CHIP\_EN configuration, it takes about 200µs for clock detection/clock switching/clock domain synchronization.

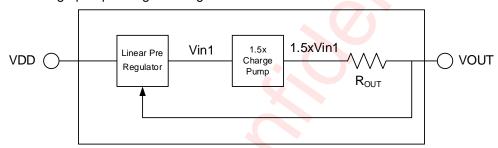

#### **Charge Pump**

#### Overview

The AW21209 is equipped with a built-in charge pump that supports 1x and 1.5x modes. The 1.5x mode can stabilize the output voltage at 4.5V in a single lithium battery system through a switched capacitor charge pump and linear regulation technology. During the charging phase, VDD charges Cfly1 and Cfly2, and during the pumping phase, the stored charges in Cfly1 and Cfly2 are transferred to VOUT. Compared with traditional switched capacitor charge pumps, AW21209 can achieve precise voltage output by adjusting the on resistance of the transfer transistor, while also having higher conversion efficiency.

#### **Output Resistance**

The model of the charge pump during boosting is shown below.

Figure 7 Charge Pump Output Resistance Model

The charge pump model is equipped with a linear pre adjustment block, a 1.5 x voltage multiplier charge pump, and an output resistor ( $R_{OUT}$ ). The typical value of ROUT is 3.5  $\Omega$ , which varies depending on the switching frequency, input voltage, flying capacitor capacitance, switch internal resistances, and capacitor ESR. The system compensates for the voltage drop caused by different load currents on  $R_{OUT}$  by adjusting Vin1, thereby stabilizing VOUT at 4.5V. As load current increases, the regulator reduces its internal voltage differential, elevating Vin1 proportionally to preserve output stability. In this state, the system operates as a closed-loop regulator until reaching current saturation-defined when Vin1 equals input voltage and the regulator enters dropout condition. Beyond this threshold, operation transitions to open-loop charge pump behavior where output voltage decreases linearly with current according to the relationship:

V<sub>OUT</sub> = 1.5 × VDD – I<sub>OUT</sub> × R<sub>OUT</sub>, maintaining predictable performance while sacrificing regulation capability.

#### LED Forward Voltage Monitoring

When the charge-pump automatic mode selection is enabled, voltages over LED drivers D1 to D6 are monitored. (Note: Power input for current source outputs D7, D8 and D9 are internally connected to the VDD pin.) Driver saturation monitor does not have a fixed voltage limit, since saturation voltage is a function of temperature and current.

#### Gain Change Hysteresis

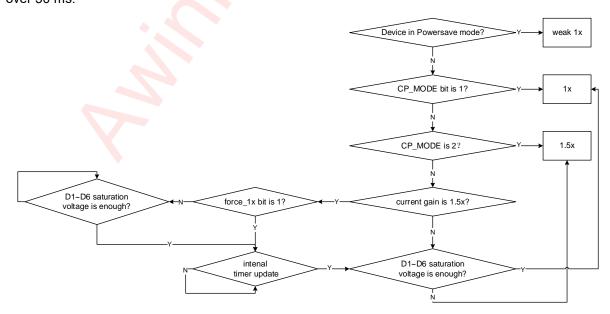

The charge-pump gain control system employs digital filtering to suppress supply voltage disturbances (such as transient voltage fluctuations during GSM bursts) from inducing unwarranted gain adjustments, while incorporating hysteresis to eliminate periodic gain variations that may arise from LED driver interactions or voltage drops inherent to 1x charge-pump operation. This dual-protection architecture features user-adjustable hysteresis thresholds, with factory-programmable default settings, enabling flexible optimization where hysteresis parameters can be minimized to near-zero levels or calibrated to precise operational requirements across various application environments. LED forward voltage monitoring and gain control block diagram is

上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

#### shown below.

Figure 8 Forward Voltage Monitoring and Gain Control Block

#### Controlled charge pump

The charge pump operation is governed by two CP\_MODE configuration bits (bits[3:2]) in the MISC register at address 36H. When both bits are set to low logic level (00), the charge pump remains disabled with its output voltage internally pulled down through a  $300 \text{k}\Omega$  resistor (typical). Any non-zero combination of these bits activates the charge pump functionality, requiring a 100us startup period when transitioning from disabled state. The device supports forced bypass mode for direct battery voltage connection to current sources, while the 1.5x boost mode elevates output voltage to 4.5V nominal through charge pump operation. In automatic mode, charge-pump operation mode is determined by saturation of constant current drivers and internal timer as shown below.

In automatic gain change mode, the charge pump is switched to bypass mode (1×), when LEDs are inactive for over 50 ms.

Figure 9 CP mode determination

上海艾为电子技术股份有眼公司 shanghai awinic technology co., ltd.

#### **Power save Mode**

#### Automatic Power save Mode

Automatic power-save mode is controlled by POWERSAVE\_EN bit in register address 36H is 1.

In automatic power-save mode, the charge pump transitions to a low-current weak 1× mode configuration. System behavior varies depending on clock source selection: when in External Clock Mode, Charge pump protection circuitry maintains active state while All analog subsystems except protection circuits are powered down; when in Internal Clock Mode, Charge pump and LED driver circuits are disabled while digital control logic remains operational to maintain system continuity.

The architecture implements a current-limited passive keep-alive circuitry that maintains output voltage at battery potential during power conservation states. Automatic power-save activation occurs when all LED driver outputs exhibit PWM signal inactivity for a continuous 50ms interval.

To prevent transient power-state transitions during program execution, the system incorporates an instruction pipeline analyzer. This feature continuously monitors execution engines 1-3, initiating power-save entry only when sustained PWM inactivity (>50ms) is detected across all LED driver outputs. It should be noted that the engine judges 50ms by counting with the clock used for program execution. If an external clock of 64kHz is used, then the 50ms here will become 25ms.

In power save mode program execution continues uninterrupted. When an instruction that requires PWM activity is executed, a fast internal-startup sequence is started automatically. If the registers related to PWM (02H/03H/06~1EH/40H/48~4AH) are accessed, the device can exit the power-saving mode.

#### PWM Power save Mode

PWM cycle power-save mode is enabled when register 36 bit [2] PWM\_PS\_EN is set to 1. The PWM Power-Save Mode (PSM) optimizes energy efficiency by deactivating analog circuitry including the Charge Pump and LED analog circuits during the PWM cycle's off-phase, while still being operable during program execution.

Unlike the Automatic Power-Save Mode that engages during PWM inactivity, this advanced mode achieves energy conservation within active PWM cycles.

When implemented with a D9-output LED operating at 50% PWM duty cycle and 5mA drive current, the PWM-PSM maintains equivalent LED brightness while significantly reducing system input current: consumption decreases to approximately 50uA during LED-off phases and stabilizes around 200uA when charge-pump-powered outputs are active, demonstrating effective power management without compromising output performance.

#### **Protection Features**

#### Thermal Shutdown (TSD)

The device features an integrated thermal shutdown protection system designed to prevent overheating damage. This system activates the LED Thermal Shutdown protocol when the junction temperature reaches 150°C and automatically resumes normal operation once the temperature decreases to 130°C. Primary activation is typically caused by excessive power dissipation, which may result from elevated input voltages and/or output currents combined with inadequate thermal management. During protective operation, thermal cycling phenomena may occur, characterized by pulsed voltage output as the system alternates between shutdown (near-zero internal power dissipation), cooling recovery, and reactivation. These cycles continue until ambient temperature reduction, input voltage optimization, current load reduction, or enhanced thermal dissipation measures are implemented. To permanently resolve thermal cycling under specified operating conditions, improved heat sinking solutions are required to achieve appropriate thermal equilibrium in relation to the device's power dissipation profile.

#### Power-On Reset (POR)

The device has internal comparators that monitor the voltages at  $V_{IN}$ . When  $V_{IN}$  is below 1.6V, reset is active and the device is in the POWERDOWN state.

#### **Error Detection**

The device has built-in LED error detection through ADC controller. Error detection does not only detect open and short circuit, but provides an opportunity to measure the VF of the LEDs. The test event is activated by a serial interface write to TEST\_CTRL(41H), and the results can be read to TEST\_ADC\_DATA(42H) through the serial interface during the next cycle. This feature can also be addressed to measure the voltage on VDD and VOUT pin. Typical example usage includes monitoring battery voltage or using INT pin as a light sensor interface.

#### Multifunctional I/O

The device has 3 I/Os, includes TRIG/INT/GPO.

TRIG is only controlled by ENGING instructions, and the pad is open-drain, which means it needs a pull-up resistor.

INT is interrupt pad in default, but it can also change to a general-output pad. User need to set INT\_CONF bit in IO\_CTRL(3BH).

GPO is a general-output pad, and its output data is controlled by GPO bit in IO\_CTRL(3BH), This feature is only applicable to AW21209FOR.

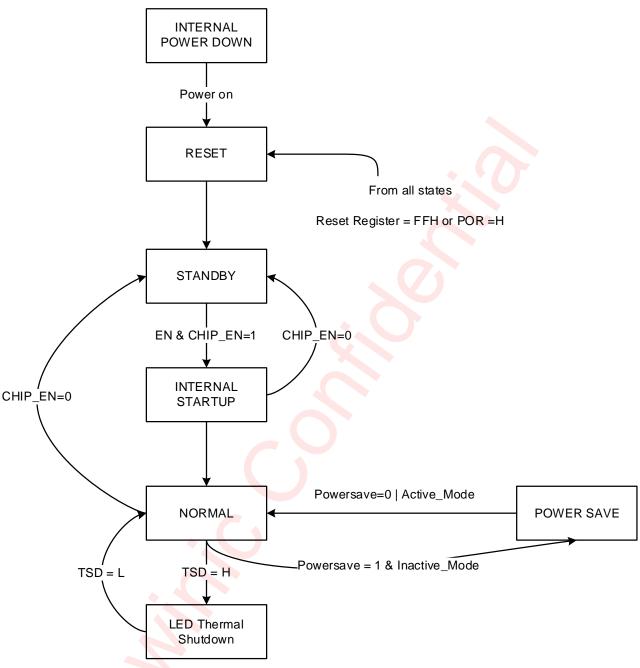

#### **Device Work Mode**

Figure 10 operating mode transition

**RESET**: In RESET mode, all internal registers are restored to their default states. The system enters RESET mode upon writing FFh to the Reset Register (3DH) or when the internal Power-On Reset (POR) circuit is activated, which occurs during initial chip power-up or when the supply voltage VDD drops below the typical threshold of 1.6V. Following VDD restoration above 2.0V (typ.), the POR function disengages, automatically transitioning the device into STANDBY mode. By default, the CHIP\_EN control bit maintains a low logic level after any POR sequence completion.

**STANDBY**: The device enters STANDBY mode when either the CHIP\_EN register bit or the EN pin is set to LOW while the Reset signal remains inactive, initiating a low-power state where all internal circuitry is deactivated. During this mode, most register settings remain writable provided the EN pin is subsequently asserted HIGH, enabling configuration updates that become operational immediately upon exiting standby (refer to the Register Details section for specific register behavior and configuration timing requirements).

STARTUP: When CHIP\_EN bit is written high and EN pin is high, the INTERNAL STARTUP SEQUENCE

Aug. 2025 V1.3

powers up all the needed internal blocks (VREF, bias, oscillator etc.). Startup delay is 100 µs.

NORMAL: During NORMAL mode the user controls the chip using the Control Registers.

**POWER SAVE**: In POWER-SAVE mode analog blocks are disabled to minimize power consumption. See Automatic Power-Save Mode section for further information.

**LED Thermal Shutdown**: In LED Thermal Shutdown mode, Charge Pump and LED output circuits will be disabled.

## **Device Program**

After power-on, the chip will perform initialization. The user must wait for 2ms before configuring Bit 6 of the CONFIG register (CHIP\_EN) to enable the chip. Only after the chip is enabled can the user configure other registers via the I²C bus. If a global soft reset is required, the user can configure the SOFT\_RESET register with the value 0xFF to trigger the soft reset. After the soft reset, the chip will restore all registers to their default values. Similar to the power-on process, the user must wait for 2ms after the soft reset is completed, then reconfigure CHIP\_EN before continuing to configure other registers via the I²C bus.

#### General I<sup>2</sup>C Operation

This device supports the I<sup>2</sup>C serial bus and data transmission protocol in fast mode at 400kHz and super-fast mode at 1000kHz. This device operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made via the open-drain I/O pins SCL and SDA. The pull-up resistor can be selected in the range of  $1k\sim10k\Omega$  and the typical value is  $4.7k\Omega$ . This device can support different high level  $(1.2V\sim5V)$  of this I<sup>2</sup>C interface.

#### **Device Address**

Table 5 I<sup>2</sup>C Device Address Configuration

| AD1 Connection | AD0 Connection | Device Address |

|----------------|----------------|----------------|

| GND            | GND            | 0x32           |

| GND            | VDD            | 0x33           |

| VDD            | GND            | 0x34           |

| VDD            | VDD            | 0x35           |

The I<sup>2</sup>C device address of AW21209 depends on the status of pins AD0 and AD1. Connecting pin AD0 or AD1 to GND or VCC will change the device address as showed in table above.

#### Data Validation

When SCL is high level, SDA level must be stable. SDA can be changed only when SCL is low level.

Figure 11 Data Validation Diagram

Aug. 2025 V1.3

#### **fC** Start/Stop

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level. I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

Figure 12 I<sup>2</sup>C Start/Stop Condition Timing

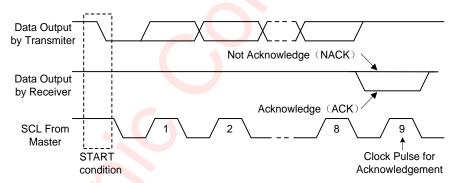

#### Acknowledge(ACK)

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends an 8-bit data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8-bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Figure 13 I<sup>2</sup>C ACK Timing

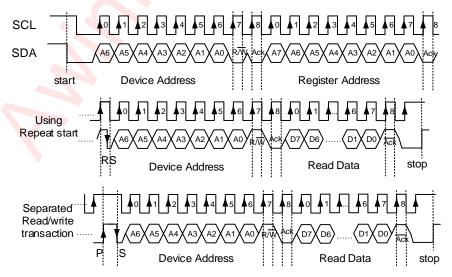

#### Write Cycle

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a start condition, a number of byte transfers (set by the software) and a stop condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends data byte to be written to the addressed register

- g) Slave sends acknowledge signal

- h) If master will send further data bytes, the control register address will be incremented by one after acknowledge signal (repeat step f and g)

- i) Master generates STOP condition to indicate write cycle end

Figure 14 I<sup>2</sup>C Write Byte Cycle

#### Read Cycle

In a read cycle, the following steps should be followed:

- a) Master device generates START condition

- b) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit (R/W = 1).

- Slave device sends acknowledge signal if the slave address is correct.

- Slave sends data byte from addressed register.

- j) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register.

- k) If the master device generates STOP condition, the read cycle is ended.

Figure 15 I<sup>2</sup>C Read Byte Cycle

上海艾为电子技术股份有限公司 shanghai awinic technology co., ltd.

## **Execution Engine Programming**

The AW21209 enables users to customize the dimming and flashing sequences of LEDs with flexibility. Each LED can be individually controlled through the serial bus, and LED drivers can also be grouped for programmed flashing patterns.

Equipped with three independent program execution engines, the AW21209 supports the creation of three distinct programmable LED banks that can be assigned to different LED drivers. Each bank can accommodate between 1 and 9 LED driver outputs.

#### **SRAM MEMORY**

The AW21209 has internal SRAM for the three LED engines. SRAM can contain up to 96 16-bit instructions (addresses 0 through 95). Memory allocation among the three LED engines is done dynamically, so that each LED engine has a separate start address and program counter (PC) that are set in the ENGINE x PROG START registers (addresses 4Ch, 4Dh, 4Eh) and ENGINE x PC registers (addresses 37h, 38h, 39h). This allows flexible memory allocation among the LED engines, and multiple engines can recall the same memory address. The PC uses relative memory addressing; when the PC is zero the engine is executing an instruction at its start address.

The register PROG MEM PAGE SEL(4Fh) select the SRAM memory page and all the SRAM memory is divided into 6 pages, each page address is from 50h to 6fh. Engines must be set to load the program mode (register 01h) before writing the SRAM.

#### PROGRAM EXECUTION ENGINE OPERATION MODES

Operation modes are defined in register ENGINE CTRL(01h). Bit[5:4] in this register define the engine1 operation mode, bit[3:2] define the engine2 operation mode and bit[1:0] define the engine3 operation mode. Each engine (1, 2, 3) operation mode can be configured separately.

#### Disabled

Each engine can be configured to disabled mode. In this mode, the engine program execution is stop and the program execution module of current engine is reset, but the content of SRAM is not affected. The PWM values are frozen and PC values are reset for current engines.

The reset time lasts approximately 1ms, so after switch to disabled mode, it is necessary to wait at least 1ms or check whether the engine busy bit(in register STATUS) is set before switching to another mode.

#### Load program

Writing to program memory is allowed only when one engine is in load program operation mode. All the three engines are stop running while one or more engines are in load program mode. PWM values are frozen and PC values are reset. Load program mode can be entered from the disabled mode only. Entering load program mode from the run program or halt mode is not allowed.

#### · Run program

Run program mode executes the instructions stored in the program memory. Register CONFIG. define how the program is executed (hold, step, free run or execute once). Register ENGINE x PC and ENG x PROG START ADDR define where the program begin to execute.

#### • Halt

Instruction execution aborts immediately, and engine operation halts. The PWM values and PC remains unchanged in this mode.

上海艾为电子技术股份有眼公司 shanghai awinic technology co., ltd.

#### PROGRAM EXECUTION ENGINE MODES

Program execution modes are defined in register CONFIG (00h). Bit[5:4] in this register define the engine1 execution mode, bit[3:2] define the engine2 execution mode and bit[1:0] define the engine3 execution mode. Each engine (1, 2, 3) operation mode can be configured separately.

#### Hold

Hold causes the execution engine to finish the current instruction and then stop. Program counter (PC) can be read or written only in this mode.

#### Step

Execute the instruction at the location pointed by the PC, increment the PC by one and then reset current engine's program execution mode to hold.

#### • Free run

Start program execution from the location pointed by the PC.

#### Execute once

Execute the instruction pointed by the current PC value and reset current engine's program execution mode to hold. The difference between step and execute once is that execute once does not increment the PC.

#### INSTRUCTION INTRODUCTION

For the three independent programmable execution engines of AW21209, users write their program blocks (consisting of many instructions) into the SRAM. Note that in order to access program memory the operation mode needs to be *load program*, at least for one of the three program execution engines. And then users can config operation mode to *run program*, these instructions will start to executed according to the program execution modes. The program execution can use the internal clock of 32.768kHz or the external clock. Next, these instructions will be introduced in detail.

#### **LED Driver Instructions**

LED Driver instruction set is listed in the following tables:

Table 6 AW21209 LED Driver Instructions

| Inst                   | Bit<br>[15] | Bit<br>[14] | Bit<br>[13] | Bit<br>[12] | Bit<br>[11] | Bit<br>[10] | Bit<br>[9]           | Bit<br>[8] | Bit<br>[7] | Bit<br>[6] | Bit<br>[5]    | Bit<br>[4] | Bit<br>[3] | Bit<br>[2] | Bit<br>[1] | Bit<br>[0]     |

|------------------------|-------------|-------------|-------------|-------------|-------------|-------------|----------------------|------------|------------|------------|---------------|------------|------------|------------|------------|----------------|

| ramp <sup>(1)</sup>    | 0           | prescale    | step time   |             |             | sign        | number of increments |            |            |            |               |            |            |            |            |                |

| ramp <sup>(2)</sup>    | 1           | 0           | 0           | 0           | 0           | 1           | 0                    | 0          | 0          | 0          | pre-<br>scale | sign       | step       | time       |            | o. of<br>ments |

| set_pwm <sup>(1)</sup> | 0           | 1           | 0           | 0           | 0           | 0           | 0                    | 0          |            |            |               | PWM        | value      |            |            |                |

| set_pwm <sup>(2)</sup> | 1           | 0           | 0           | 0           | 0           | 1           | 0                    | 0          | 0          | 1          | 1             | 0          | 0 0 PWM    |            | l value    |                |

| wait                   | 0           | prescale    |             |             | time        |             |                      | 0          | 0          | 0          | 0             | 0          | 0          | 0          | 0          | 0              |

<sup>(1)</sup> This opcode is used with numerical operands.

#### Ramp

This instruction facilitates a smooth transition between one PWM value and another on the D1 to D9 outputs, effectively generating ramps with either a negative or positive slope. The AW21209 supports programming both extremely fast and extremely slow ramps.

The ramp instruction facilitates the generation of a PWM ramp, utilizing the effective PWM value as the starting point. At each ramp step, the output is incremented or decremented by one unit unless the number of increments is set to zero. The time span for a single ramp step is determined by the prescale bit [14] and the

<sup>(2)</sup> This opcode is used with variables.

#### 上海艾为电子技术股份有眼公司 shanghai awinic technology co., ltd.

step time bits [13:9]. Specifically, when the prescale is configured to 0, the cycle time is set to 0.49 ms, and when the prescale is configured to 1, the cycle time is set to 15.6 ms. Consequently, the minimum time span for a single step is 0.49 ms (prescale  $\times$  step time span = 0.49 ms  $\times$  1), while the maximum time span is 15.6 ms  $\times$  31 = 484 ms.

The number of increments specifies the total steps taken during a single ramp instruction. The maximum increment value is 255, representing a progression from the zero value to the maximum value. If the PWM reaches its minimum or maximum value (0 or 255) during the ramp instruction, the instruction will continue to completion regardless of saturation. The ramp instruction governs the eight most-significant bits (MSB) of the PWM values, while the remaining bits are internally interpolated as intermediate ramp values to ensure a smoother transition. This functionality allows the ramp instruction to serve as both a ramp and a wait instruction. Note: The ramp instruction functions as a wait instruction when the increment bits [7:0] are set to zero.

Programming ramps using variables closely mirrors the process of programming ramps with numerical operands. The sole distinction lies in capturing the step time and number of increments from variable registers at the onset of instruction execution. Any updates to the variables after the initiation of instruction execution will not influence the ongoing process. Furthermore, during each ramp step, the output is incremented or decremented by one unit, provided the increment value is not zero. The duration of a single step is determined by the prescale and step time bits. Step time can be specified using variables A, B, C, or D. Variables A, B, and C are configured via the ld instruction, whereas Variable D serves as a global variable that can be set by writing to the VARIABLE register (address 3C). Additionally, the LED TEST ADC register (address 42) can also serve as a source for Variable D. It should be noted that Variable D is the sole local variable accessible for reading across the serial bus. Naturally, the variable stored at address 3Ch is also readable (and writable).

| NAME                      | VALUE(d) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| procedo                   | 0        | Divides master clock (32.7 kHz) by 16 = 2048 Hz, 0.488 ms cycle time                                                                                                                                                                                                                                                                                                            |

| prescale                  | 1        | Divides master clock (32.7 kHz) by 512 = 64 Hz, 15.625 ms cycle time                                                                                                                                                                                                                                                                                                            |

| -1                        | 0        | Increase PWM output                                                                                                                                                                                                                                                                                                                                                             |

| sign                      | 1        | Decrease PWM output                                                                                                                                                                                                                                                                                                                                                             |

| step time(1)              | 1-31     | One ramp increment done in (step time) x (clock after prescale)                                                                                                                                                                                                                                                                                                                 |

| increments <sup>(1)</sup> | 0-255    | The number of increment/decrement cycles. Note: Value 0 takes the same time as increment by 1, but it is the wait instruction                                                                                                                                                                                                                                                   |

| step time <sup>(2)</sup>  | 0-3      | One ramp increment done in (step time) × (prescale).  Step time is loaded with the value (5 LSB bits) of the variable defined below.  0 = local variable A  1 = local variable B  2 = global variable C  3 = register address 3CH variable D value, or register address 42H value.  The value of the variable should be from 00001b to 11111b (1d to 31d) for correct operation |

| increments <sup>(2)</sup> | 0-3      | The number of increment/decrement cycles. Value is taken from variable following defined:  0 = local variable A  1 = local variable B  2 = global variable C  3 = register address 3CH variable D value, or register address 42H value.                                                                                                                                         |

<sup>(1)</sup> Valid for numerical operands.

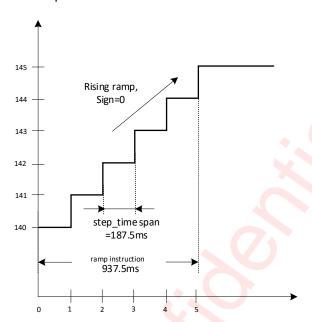

#### **Ramp Instruction Application Example**

Suppose that the LED dimming is controlled according to the linear scale and effective PWM value at the moment t = 0 is 140d (approximately 55%), as shown in Figure 25, and goal is to reach a PWM value of 145d (approximately 57%) at the moment t = 937.5ms. The parameters for the RAMP instruction are:

Prescale = 1 → 15.625 ms cycle time

<sup>(2)</sup> Valid for variables.

Aug. 2025 V1.3

- Step time =  $12 \rightarrow \text{step time span is } 12 \times 15.625 \text{ ms} = 187.5 \text{ ms}$

- Sign = 0 → increase PWM output

- # of increments = 5 → take 5 steps

Figure 16 Example of ramp commands

#### Set PWM

This instruction is designed to set the PWM value on outputs D1 through D9 without employing any ramping functionality. The PWM output value can be configured within the range of 0 to 255 using the PWM value bits [7:0]. Execution of this instruction requires sixteen clock cycles.

| NAME                         | VALUE(d) | DESCRIPTION                                                                                                                              |  |  |  |  |

|------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PWM value (i) <sup>(1)</sup> | 0-255    | PWM output duty cycle 0 - 100%                                                                                                           |  |  |  |  |

| variable (ii) <sup>(2)</sup> | 0-3      | 0 = local variable A 1 = local variable B 2 = global variable C 3 = register address 3CH variable D value, or register address 42H value |  |  |  |  |

<sup>(1)</sup> Valid for numerical operands.

#### Wait

When a wait instruction is executed, the engine enters the wait state, and the PWM values on the outputs are held constant.

| NAME     | VALUE(d) | DESCRIPTION                                                                 |

|----------|----------|-----------------------------------------------------------------------------|

| prescale | 0        | Divide master clock (32.7 kHz) by 16 which means 0.488 ms cycle time.       |

| prescale | 1        | Divide master clock (32.7 kHz) by 512 which means 15.625 ms cycle time.     |

| time     | 1-31     | Total wait time is = (time) x (prescale). Maximum 484 ms, minimum 0.488 ms. |

#### Clock

Clock frequency adjustment affects the instruction execution cycle, the ramp instruction ramp – up\ ramp – down time, and the wait instruction waiting time. An instruction is 16 bits, and its execution requires 16 clock cycles. The instruction execution can use an internal clock of 32.768 kHz, or an external clock of 32 kHz or 64 kHz.

<sup>(2)</sup> Valid for variables.

#### 上海又万电子孩爪股份有眼公司 shanghai awinic technology co., ltd.

| clock                        | instruction execution cycle       |

|------------------------------|-----------------------------------|

| internal clock of 32.768 kHz | 16 * 1 / 32768Hz * 1000 = 0.488ms |

| external clock of 32 kHz     | 16 * 1 / 32000Hz * 1000 = 0.5ms   |

| external clock of 64 kHz     | 16 * 1 / 64000Hz * 1000 = 0.25ms  |

Both the ramp and wait instructions have a prescale parameter, which is related to the clock cycle. Take the ramp instruction as an example.

| clock                          |   | prescale                                                              |

|--------------------------------|---|-----------------------------------------------------------------------|

| internal clock of 32,768 kHz   | 0 | Divides master clock (32.768kHz) by 16 = 2048 Hz, 0.488 ms cycle time |

| internal clock of 32.700 ki iz | 1 | Divides master clock (32.768kHz) by 512 = 64 Hz, 15.625 ms cycle time |

| external clock of 32 kHz       | 0 | Divides master clock (32kHz) by 16 = 2000 Hz, 0.5 ms cycle time       |

| external clock of 32 kHz       | 1 | Divides master clock (32kHz) by 512 = 62.5 Hz, 16 ms cycle time       |

| external clock of 64 kHz       | 0 | Divides master clock (64kHz) by 16 = 4000 Hz, 0.25 ms cycle time      |

| external clock of 64 kHz       | 1 | Divides master clock (64kHz) by 512 = 125 Hz, 8 ms cycle time         |

#### **LED Mapping Instructions**

LED Mapping instruction set is listed in the following tables:

Table 7 AW21209 LED Mapping Instructions

| Inst          | Bit<br>[15] | Bit<br>[14] | Bit<br>[13] | Bit<br>[12] | Bit<br>[11] | Bit<br>[10] | Bit<br>[9] | Bit<br>[8] | Bit<br>[7] | Bit<br>[6]        | Bit<br>[5] | Bit<br>[4] | Bit<br>[3] | Bit<br>[2] | Bit<br>[1] | Bit<br>[0] |

|---------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|------------|------------|-------------------|------------|------------|------------|------------|------------|------------|

| mux_ld_start  | 1           | 0           | 0           | 1           | 1           | 1           | 1          | 0          | 0          |                   |            | SRAM       | addres     |            |            |            |

| mux_map_start | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 0          | 0          |                   |            | SRAM       | addres     | ss 0-95    |            |            |

| mux_ld_end    | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 0          | 1          |                   |            | SRAM       | addres     | s 0-95     |            |            |

| mux_sel       | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 1          | 0          | LED select        |            |            |            |            |            |            |

| mux_clr       | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 1          | 0          | 0                 | 0          | 0          | 0          | 0          | 0          | 0          |

| mux_map_next  | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 1          | 1          | 0                 | 0          | 0          | 0          | 0          | 0          | 0          |

| mux_map_prev  | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 1          | 1          | 1                 | 0          | 0          | 0          | 0          | 0          | 0          |

| mux_ld_next   | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 1          | 1          | 0                 | 0          | 0          | 0          | 0          | 0          | 1          |

| mux_ld_prev   | 1           | 0           | 0           | 1           | 1           | 1           | 0          | 1          | 1          | 1                 | 0          | 0          | 0          | 0          | 0          | 1          |

| mux_ld_addr   | 1           | 0           | 0           | 1           | 1           | 1           | 1          | 1          | 0          | SRAM address 0-95 |            |            |            |            |            |            |

| mux_map_addr  | 1           | 0           | 0           | 1           | 1           | 1           | 1          | 1          | 1          | SRAM address 0-95 |            |            |            |            |            |            |

These instructions define the engine-to-LED mapping. The mapping information is stored in a table, which is stored in the SRAM (program memory of the AW21209). AW21209 has three program execution engines which can be mapped to 9 LED drivers or to one GPO pin. One engine can control one or multiple.

LED drivers. There are totally eleven instructions for the engine-to-LED-driver control: mux\_ld\_start, mux\_map\_start, mux\_ld\_end,mux\_sel, mux\_clr, mux\_map\_next, mux\_map\_prev, mux\_ld\_next, mux\_ld\_prev, mux\_ld\_addr and mux\_map\_addr.

Mapping table in SRAM.

|                          | Bit                         | Bit  | Bit  | Bit  | Bit  | Bit  | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit | Bit |

|--------------------------|-----------------------------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                          | [15]                        | [14] | [13] | [12] | [11] | [10] | [9] | [8] | [7] | [6] | [5] | [4] | [3] | [2] | [1] | [0] |

| mapping table<br>in SRAM | GPO(only<br>AW21209<br>FOR) |      |      |      |      |      |     | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  |

上海文列电子技术股份有限公司 shanghai awinic technology co., ltd.

#### MUX\_LD\_START; MUX\_LD\_END

The instructions mux ld start and mux ld end are utilized to specify the memory location of the mapping table.

| NAME         | VALUE(d) | DESCRIPTION                     |

|--------------|----------|---------------------------------|

| SRAM address | 0-95     | Mapping table start/end address |

#### **MUX MAP START**

Mux\_map\_start specifies the starting address of the mapping table in memory, and simultaneously activates (maps) the first row of the table.

| NAME         | VALUE(d) | DESCRIPTION                 |

|--------------|----------|-----------------------------|

| SRAM address | 0-95     | Mapping table start address |

#### MUX\_SEL

The mux\_sel instruction enables the connection of exactly one LED driver (or the GPO pin) to a program execution engine. To connect multiple LEDs to a single engine, the mapping table is utilized. Once the mapping for an LED has been released, the PWM register value continues to control the LED brightness. If the mapping for the GPO pin is released, serial bus control assumes responsibility for managing the GPO state.

| NAME       | VALUE(d) | DESCRIPTION                                             |

|------------|----------|---------------------------------------------------------|

|            |          | 0 = no drivers selected                                 |

|            |          | 1 = LED1 selected                                       |

| LED select | 0-16     | 2 = LED2 selected                                       |

| LLD 30lcct | 0-10     |                                                         |

|            |          | 9 = LED9 selected                                       |

|            |          | 16 = GPO, This feature is only applicable to AW21209FOR |

#### **MUX CLR**

Mux\_clr instruction clears the mapping between the engine and the driver. Once the mapping for an LED has been released, the PWM register continues to control the LED brightness. If the mapping for the GPO pin is released, serial bus control assumes responsibility for managing the GPO state.

#### MUX\_MAP\_NEXT

This instruction activates the next row in the mapping table each time it is invoked. For instance, if the second row is currently active, invoking the mux\_map\_next instruction will activate the third row. If the end address of the mapping table is reached, activation will roll back to the start address of the mapping table upon the next invocation of the mux\_map\_next instruction. The engine does not push a new PWM value to the LED driver output until either the set\_pwm or ramp instruction is executed. Once the mapping for an LED has been released, the value stored in the PWM register continues to control the LED brightness. If the mapping for the GPO pin is released, serial bus control assumes responsibility for managing the GPO state.

#### MUX\_LD\_NEXT

Similar to the mux\_map\_next instruction, this instruction only updates the index pointer to point to the next row in the mapping table. However, no actual mapping is established, and the connection between the engine and the LED driver remains unchanged.

#### **MUX MAP PREV**

This instruction activates the previous row in the mapping table each time it is invoked. For instance, if the third row is currently active, invoking the mux\_map\_prev instruction will activate the second row. If the start address of the mapping table is reached, activation will roll to the end address of the mapping table upon the next invocation of the mux\_map\_prev instruction. The engine does not push a new PWM value to the LED driver output until either the set\_pwm or ramp instruction is executed. Once the mapping for an LED has been released, the value stored in the PWM register continues to control the LED brightness. If the mapping for the GPO pin is released, serial bus control assumes responsibility for managing the GPO state.

#### MUX\_LD\_PREV

Similar to the mux\_map\_prev instruction, this instruction only updates the index pointer to point to the previous

上海艾为电子技术股份有眼公司 shanghai awinic technology co., ltd.

row in the mapping table. However, no actual mapping is established, and the connection between the engine and the LED driver remains unchanged.

#### MUX\_MAP\_ADDR

The mux\_map\_addr instruction sets the index pointer to point to the row in the mapping table defined by bits [6:0] and activates the specified row. The engine does not push a new PWM value to the LED driver output until either the set\_pwm or ramp instruction is executed. Once the mapping for an LED has been released, the value stored in the PWM register continues to control the LED brightness. If the mapping for the GPO pin is released, serial bus control assumes responsibility for managing the GPO state.

| NAME         | VALUE(d) | DESCRIPTION                               |  |

|--------------|----------|-------------------------------------------|--|

| SRAM address | 0-95     | Any SRAM address containing mapping data. |  |

#### MUX LD ADDR

The Mux\_ld\_addr instruction sets the index pointer to point to the row in the mapping table defined by bits [6:0], but the specified row is not activated.

| NAME         | VALUE(d) | DESCRIPTION                               |

|--------------|----------|-------------------------------------------|

| SRAM address | 0-95     | Any SRAM address containing mapping data. |

#### **Branch Instructions**

LED Branch instruction set is listed in the following tables:

Table 8 AW21209 Branch Instructions

| Inst                  | Bit<br>[15] | Bit<br>[14] | Bit<br>[13] | Bit<br>[12]  | Bit<br>[11]                                                                | Bit<br>[10]      | Bit [9] | Bit<br>[8]                                                                           | Bit<br>[7] | Bit<br>[6]   | Bit<br>[5]       | Bit<br>[4]       | Bit<br>[3] | Bit<br>[2] | Bit<br>[1] | Bit<br>[0] |  |

|-----------------------|-------------|-------------|-------------|--------------|----------------------------------------------------------------------------|------------------|---------|--------------------------------------------------------------------------------------|------------|--------------|------------------|------------------|------------|------------|------------|------------|--|

| rst                   | 0           | 0           | 0           | 0            | 0                                                                          | 0                | 0       | 0                                                                                    | 0          | 0            | 0                | 0                | 0          | 0          | 0          | 0          |  |

| branch <sup>(1)</sup> | 1           | 0           | 1           |              |                                                                            | loop c           | ount    |                                                                                      |            |              |                  | step             | number     |            |            |            |  |

| branch <sup>(2)</sup> | 1           | 0           | 0           | 0            | 0                                                                          | 1                | 1       |                                                                                      |            | st           | ep num           | ber              |            |            | loop       | count      |  |