# **LIN Interface General Purpose MCU**

# **Features**

- Operating voltage range: 6V~18V, load dump voltage: 45V

- 32-bit MCU

- Maximum operating frequency: 16MHz

- 64KB FLASH, with erase protection function

- 16KB SRAM memory

- 4-channel 16bit PWM current sinks, maximum 60mA/channel

- Support LS junction voltage (0V~8V) detection, support LS temperature compensation

- 12 general GPIO ports

- Support PWM mode

- Support external LIN transceiver multiplexing function

- Integrated LIN transceiver, support automatic addressing function

- Support SAE J2602/LIN2.x protocol LIN slave interface

- 1 WDT and 1 WWDG

- 2 Basic Timers, 1 General-Purpose Timer, 1

Wakeup Timer

- 1 I<sup>2</sup>C, 1 SPI, 1 UART

- 12-bit ADC converter, supporting 13 channels

- Optional reference voltage (1.2V/2.4V/3.3V)

- Temperature sensor

- VBAT voltage detection

- LS junction voltage detection

- Support for SWD debugging

- Support Power on Reset (POR) and Brown out Reset (BOR) function

- Operation range: -40~125°C

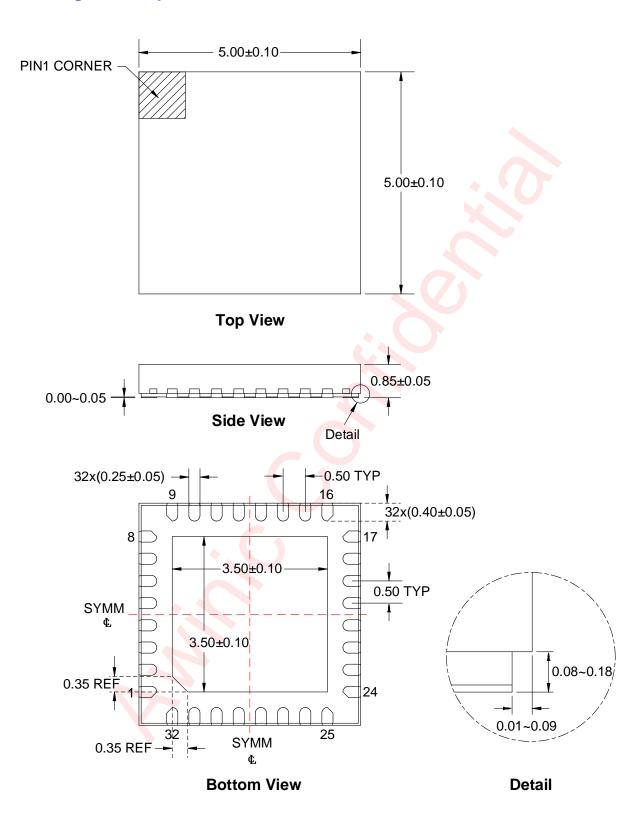

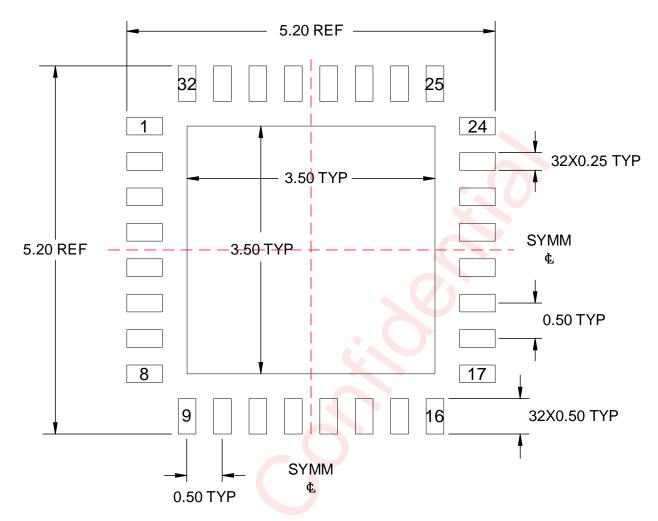

- Package: QFN 5x5-32L

# **General Description**

AW32F020QNR-Q1 is a chip designed specifically for automotive window motor controllers, which can improve the convenience of debugging automotive window controls.

The AW32F020QNR-Q1 integrates a 32-bit MCU. The MCU provides superior computational performance and an efficient interrupt system, while the peripheral devices use a smaller number of pins and lower power consumption.

AW32F020QNR-Q1 integrates 64KB FLASH memory with erase/write protection function. The LIN communication module is integrated to support the transceiver function of LIN communication.

Integrated 12-bit ADC for LS junction voltage and temperature detection, supporting 13 channels, VREF voltage can be configured to 1.2V/2.4V/3.3V.

Support 4 high voltage current sinks, the maximum current of each channel is up to 60mA. Support 16-bit PWM dimming, support 80Hz~250Hz dimming frequency.

Two basic timers, one general-purpose timer and one WDT are integrated. 12 general GPIO ports are integrated to support PWM mode and external LIN receiver interconnection. Support one hardware I2C or SPI or UART.

The SWD debug interface is integrated with built-in Power on Reset (POR) and Brown out Reset (BOR) functions to effectively protect the chip.

AW32F020QNR-Q1 is packaged in QFN 5x5-32L.

# **Applications**

Automotive motor control

Electric window control

Electric seat control

Automotive LED driver

Door locks

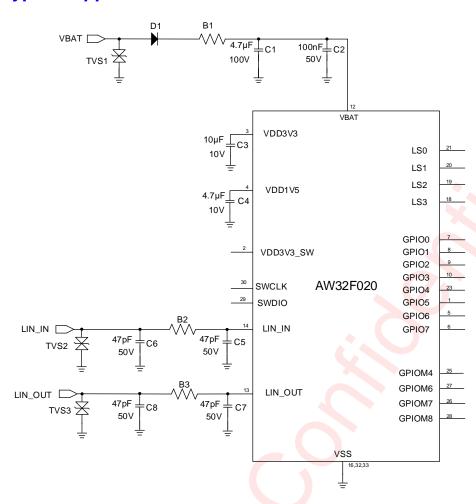

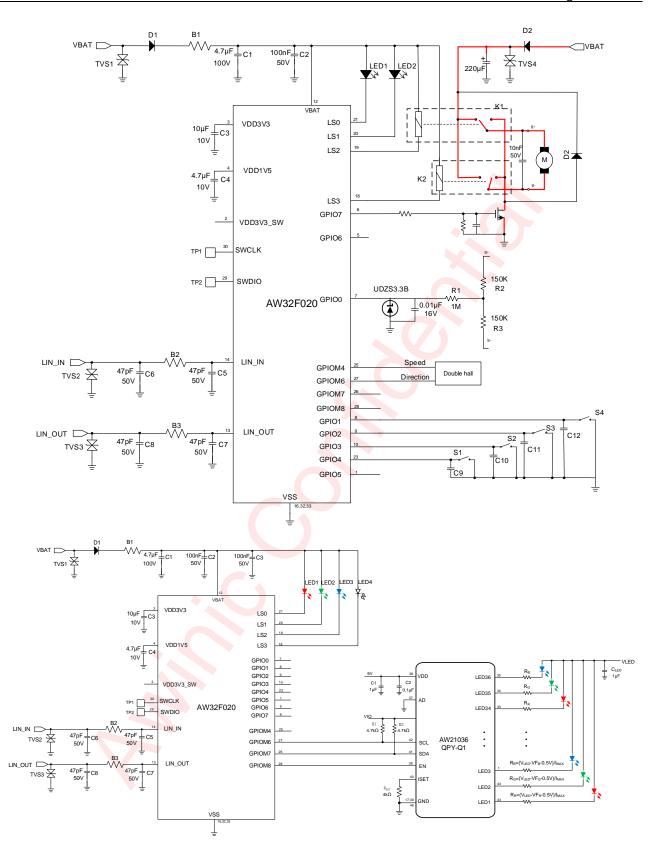

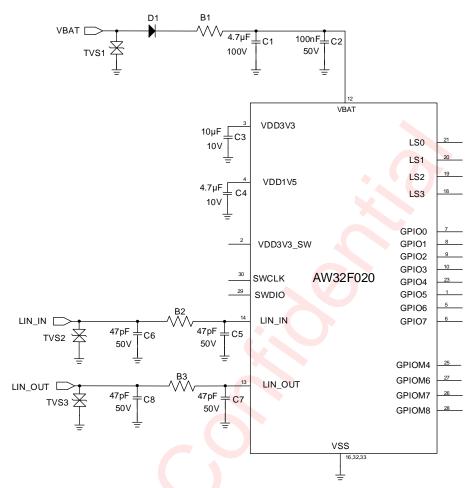

# **Typical Application Circuit**

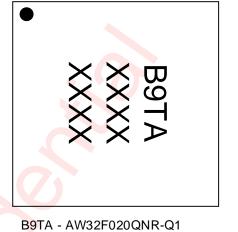

# **Pin Configuration And Top Mark**

AW32F020QNR-Q1

#### (Top View) 31 30 29 28 27 26 25 GPI05 (24 NC 2) (23 VDD3V3\_SW GPIO4 3) (22 VDD3V3 NC (21) VDD1V5 4) LS0 33 5) (20) GPIO6 LS1 GPI07 <u>6</u>) (19 LS2 7 GPIO0 LS3 GPIO1 (<u>8</u>) (17 NC 12 13 14 15 16 VSS S

# AW32F020QNR-Q1 Marking (Top View)

B9TA - AW32F020QNR-Q1

XXXX/XXXX - Production Tracing Code

Figure 1 Pin Configuration and Top Marking

# **Pin Definition**

| No. | NAME      | DESCRIPTION                                      |

|-----|-----------|--------------------------------------------------|

| 1   | GPIO5     | General purpose IO. ADC_IN/PWM_OUT               |

| 2   | VDD3V3_SW | LDO output 3.3V, 10mA max. Closed in sleep mode. |

| 3   | VDD3V3    | Connect to the external 10µF capacitor.          |

| 4   | VDD1V5    | Connect to the external 4.7µF capacitor.         |

| 5   | GPIO6     | General purpose IO.                              |

| 6   | GPIO7     | General purpose IO.                              |

| 7   | GPIO0     | General purpose IO. ADC_IN/PWM_OUT.              |

| 8   | GPIO1     | General purpose IO. ADC_IN/PWM_OUT.              |

| 9   | GPIO2     | General purpose IO. ADC_IN/PWM_OUT.              |

| 10  | GPIO3     | General purpose IO. ADC_IN/PWM_OUT.              |

| 11  | NC        | No connect.                                      |

| 12  | VBAT      | Supply voltage.                                  |

| 13  | LIN_OUT   | J2602 LIN 2.x.                                   |

| 14  | LIN_IN    | J2602 LIN 2.x.                                   |

| 15  | NC        | No connect.                                      |

| 16  | VSS       | Ground.                                          |

| 17 | NC     | No connect.                                                                 |

|----|--------|-----------------------------------------------------------------------------|

| 18 | LS3    | Low-side switch. PWM_OUT.                                                   |

| 19 | LS2    | Low-side switch. PWM_OUT.                                                   |

| 20 | LS1    | Low-side switch. PWM_OUT.                                                   |

| 21 | LS0    | Low-side switch. PWM_OUT.                                                   |

| 22 | NC     | No connect.                                                                 |

| 23 | GPIO4  | General purpose IO. ADC_IN/PWM_OUT.                                         |

| 24 | NC     | No connect.                                                                 |

| 25 | GPIOM4 | General purpose IO, TIM3_CH1/SPI_MISO/PWM_OUT.                              |

| 26 | GPIOM7 | General purpose IO, TIM3_CH3/UART_TX/I <sup>2</sup> C_SDA/SPI_MOSI/PWM_OUT. |

| 27 | GPIOM6 | General purpose IO, TIM3_CH2/UART_RX/I <sup>2</sup> C_SCL/SPI_SCK/PWM_OUT.  |

| 28 | GPIOM8 | General purpose IO, TIM3_CH4/SPI_CS/PWM_OUT.                                |

| 29 | SWDIO  | Debugger data. Integrated weak pull up.                                     |

| 30 | SWCLK  | Debugger clk. Integrated weak pull up.                                      |

| 31 | NC     | No connect.                                                                 |

| 32 | VSS    | Ground.                                                                     |

| 33 | VSS    | Ground.                                                                     |

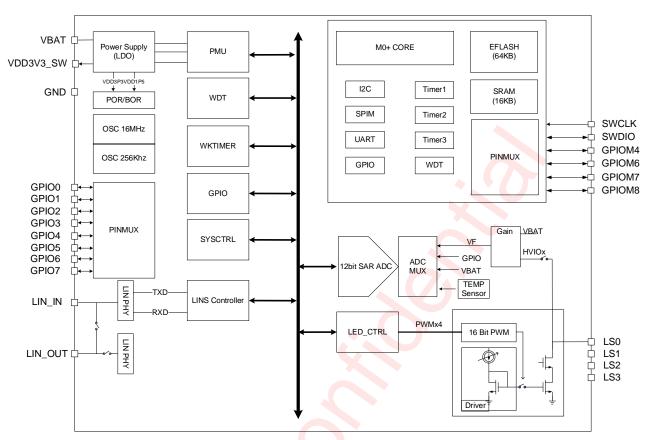

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2 Function Block Diagram

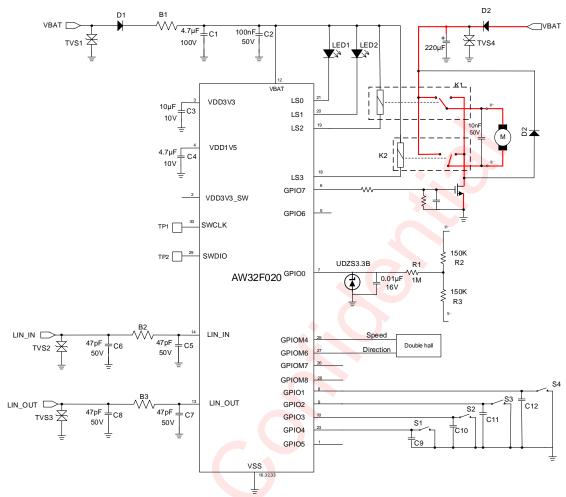

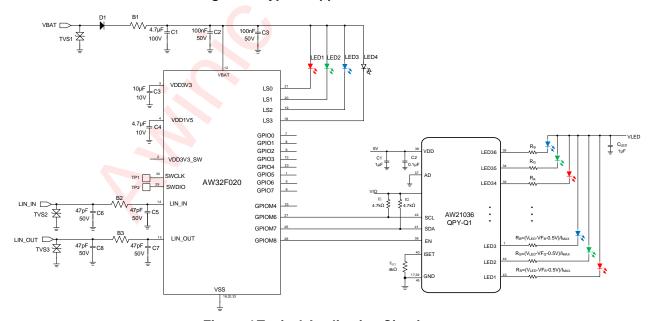

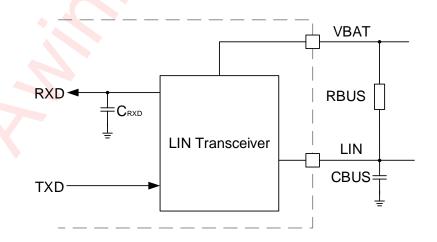

# TYPICAL APPLICATION CIRCUITS

Figure 3 Typical Application Circuit

Figure 4 Typical Application Circuit

awinic

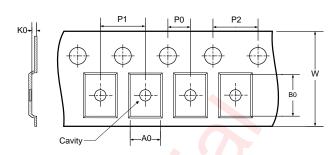

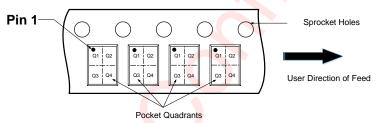

| Part Number    | Temperature | Package              | Marking | Moisture<br>Sensitivity Level | Environmental<br>Information | Delivery Form                |

|----------------|-------------|----------------------|---------|-------------------------------|------------------------------|------------------------------|

| AW32F020QNR-Q1 | -40°C∼125°C | QFN 5mm X<br>5mm-32L | В9ТА    | MSL3                          | ROHS+HF                      | 6000 units/<br>Tape and Reel |

# **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PARAME <sup>-</sup>            | TERS                                            | RANGE          |  |

|--------------------------------|-------------------------------------------------|----------------|--|

|                                | 500ms                                           | -0.3V to 45V   |  |

|                                | 5min                                            | -0.3V to 28V   |  |

|                                | 5ms                                             | -1.1V          |  |

|                                | 20ns                                            | -4V            |  |

|                                | ISO 7637-2 pulse 1,                             |                |  |

|                                | VBAT=13.5V, TA=(23±5)°C                         | -112V          |  |

| VBAT                           | ISO 7637-2 pulse 2a,                            | 55V            |  |

|                                | VBAT=13.5V, TA=(23±5)°C                         | 33V            |  |

|                                | ISO 7637-2 pulse 2b,                            | 10V            |  |

|                                | VBAT=13.5V, TA=(23±5)°C<br>ISO 7637-2 pulse 3a, |                |  |

|                                | VBAT=13.5V, TA=(23±5)°C                         | -165V          |  |

|                                | ISO 7637-2 pulse 3b,                            |                |  |

|                                | VBAT=13.5V, TA=(23±5)℃                          | 112V           |  |

|                                | 500ms                                           | -40V to 40V    |  |

|                                | ISO 7637-3 pulse +2a,                           | 5V             |  |

|                                | VBAT=13.5V, TA=(23±5)°C                         | 50             |  |

| LIN_IN, LIN_OUT                | ISO 7637-3 pulse -2a,                           | -5v            |  |

|                                | VBAT=13.5V, TA=(23±5)°C<br>ISO 7637-3 pulse 3a, |                |  |

|                                | VBAT=13.5V, TA=(23±5)°C                         | -80V           |  |

|                                | ISO 7637-3 pulse 3b,                            |                |  |

|                                | VBAT=13.5V, TA=(23±5)°C                         | 60V            |  |

|                                | 500ms                                           | -0.3V to 45V   |  |

| 1.0%                           | 5min                                            | -0.3V to 28V   |  |

| LSx                            | 5ms                                             | -1.1V          |  |

|                                | 20ns                                            | -4V            |  |

| VBAT, LIN_IN, LI               | N_OUT, LSx                                      | -0.3V to 24V   |  |

| GPIOx, SWDCI                   | K, SWDIO                                        | -0.3V to 3.6V  |  |

| Junction-to-ambient the        | rmal resistance θ <sub>JA</sub>                 | 52.3°C /W      |  |

| Maximum operating juncti       | on temperature T <sub>JMAX</sub>                | 150°C          |  |

| Storage temper                 | ature T <sub>STG</sub>                          | -55°C to 150°C |  |

| Lead temperature (solo         | lering 10 seconds)                              | 260°C          |  |

|                                | ESD(Including CDM HBM)(N                        | OTE 2)         |  |

| VBAT/LIN_IN/LIN_O              | VBAT/LIN_IN/LIN_OUT to GND HBM                  |                |  |

| (Test condition: AEC-          | (Test condition: AEC-Q100-002-RevE)             |                |  |

| Other PINS HBM (Test condition | on: AEC-Q100-002-RevE)                          | ±2kV           |  |

| CDM (Test condition: AE        | C-Q100-011-RevD)                                | ±750V          |  |

|                                | Latch-Up                                        |                |  |

| Test condition: AEC Q100-004 | +IT: 450mA  |

|------------------------------|-------------|

| Test condition. AEC_Q100-004 | -IT: -450mA |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin.

# **Recommended Operating Conditions**

| Symbol           | Parameter                            | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------|------|------|------|------|

| V <sub>BAT</sub> | Input voltage                        | 6    | 13.5 | 18   | V    |

| C <sub>1</sub>   | Input capacitance connected to VBAT  | 2.2  | 4.7  | 10   | μF   |

| C <sub>2</sub>   | Input capacitance connected to VBAT  |      | 0.1  |      | μF   |

| C <sub>3V3</sub> | Capacitance connected to VDD3V3      | 4.7  |      | 10   | μF   |

| C <sub>1V5</sub> | Capacitance connected to VDD1V5      | 1    |      | 4.7  | μF   |

| TA               | Operating free-air temperature range | -40° | 25   | 125  | °C   |

# **ELECTRICAL CHARACTERISTICS**

VBAT=6V to 18V, T<sub>A</sub>=25°C for typical values (unless otherwise noted)

| PARAMETER                          | TEST CONDITION                                                      | MIN  | TYP  | MAX  | UNIT   |

|------------------------------------|---------------------------------------------------------------------|------|------|------|--------|

| Operation Conditions               |                                                                     |      |      |      |        |

| VBAT                               |                                                                     | 6    | 13.5 | 18   | V      |

| IO Supply(VDD3V3)                  |                                                                     | 2.97 | 3.3  | 3.63 | V      |

| ASIC Core Supply                   |                                                                     | 2.97 | 3.3  | 3.63 | V      |

| MCU Core Supply                    | MCU Core Supply including SRAM and Flash                            | 1.4  | 1.55 | 1.65 | V      |

| FLASH Memory                       |                                                                     |      |      |      |        |

| Sector Endurance                   |                                                                     | 20k  |      |      | cycles |

| Data Retention                     | @25°C                                                               | 100  |      |      | Years  |

| Data Retention                     | @85°C                                                               | 25   |      |      | Years  |

| SRAM                               |                                                                     |      |      |      |        |

| Min Retention Voltage              | Minimum Retention Voltage below which SRAM data are not guaranteed. | 1.35 |      |      | V      |

| CLOCKs                             |                                                                     |      |      |      |        |

| System RC Oscillator Frequency     | 70                                                                  |      | 16   |      | MHz    |

| System RC Oscillator<br>Accuracy   | 16MHz                                                               | -3   |      | 3    | %      |

| System RC Oscillator start up time | ·. C)                                                               |      | 10   |      | μs     |

| Auxiliary system clock             | Used in sleep mode                                                  |      | 256  |      | kHz    |

| Auxiliary system clock<br>Accuracy |                                                                     | -10  |      | 10   | %      |

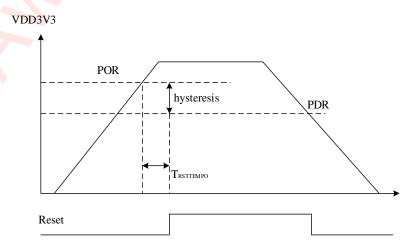

| POR/BOR                            |                                                                     |      |      |      |        |

| POR power-on detection threshold   | Triggered by VDD3V3 power-on                                        | 2.1  | 2.4  | 2.7  | V      |

| POR power-on detection hysteresis  |                                                                     |      | 0.2  |      | V      |

|                                    |                                                                     | 2.4  | 2.55 | 2.7  |        |

|                                    | T: 11 1/250/20                                                      | 2.5  | 2.65 | 2.8  |        |

| Under Voltage Threshold of BOR     | Triggered by VDD3V3 power-off, user configurable                    | 2.6  | 2.75 | 2.9  | V      |

| Threshold of BOIX                  | a.c comigaranto                                                     | 2.7  | 2.85 | 3    |        |

|                                    |                                                                     | 2.8  | 2.95 | 3.1  |        |

| Battery Monitor                    |                                                                     |      |      |      |        |

| Under Voltage                      | Triggered by VBAT power-off,                                        | 4.5  | 5.0  | 5.5  | V      |

| PARAMETER                           | TEST CONDITION                                              | MIN  | TYP    | MAX   | UNIT |

|-------------------------------------|-------------------------------------------------------------|------|--------|-------|------|

| Threshold                           | generates interrupt to MCU(except in                        |      |        |       |      |

|                                     | sleep mode), user configurable                              | 5.5  | 6.0    | 6.5   | V    |

|                                     |                                                             | 6.5  | 7.0    | 7.5   | V    |

|                                     |                                                             | 7.5  | 8.0    | 8.5   | V    |

|                                     |                                                             | 8.5  | 9.0    | 9.5   | V    |

| Under Voltage<br>hysteresis         | The under voltage threshold is set to 5V, user configurable | 0.01 | 0.125  | 0.255 | V    |

| Under Voltage Digital debounce time | User configurable, the step size is 62.5ns or 62.5µs        |      |        | 16.32 | ms   |

|                                     |                                                             | 21   | 22.5   | 24    |      |

|                                     |                                                             | 23.5 | 25     | 26.5  |      |

|                                     | Triggered by VBAT power-on,                                 | 26   | 27.5   | 29    |      |

| Over Voltage<br>Threshold           | Generates interrupt to MCU(except in                        | 28.5 | 30     | 31.5  | V    |

| Tilloshold                          | sleep mode), user configurable                              | 31   | 32.5   | 34    |      |

|                                     |                                                             | 33.5 | 35     | 36.5  |      |

|                                     |                                                             | 36   | 37.5   | 39    |      |

| Over Voltage<br>Hysteresis          | The over voltage threshold is set to 25V, user configurable | 0.04 | 0.714  | 1.624 | V    |

| Over Voltage Digital debounce time  | User configurable, the step size is 62.5ns or 62.5µs        |      |        | 16.32 | ms   |

| Current Source (LS)                 |                                                             |      |        |       |      |

| LS Dropout Voltage                  | The voltage when the current drops to 90%(60mA)             |      |        | 1.6   | V    |

| Sink Current                        | VBAT>6V                                                     | 0.12 |        | 60    | mA   |

| Sink Current step size              |                                                             |      | 120    |       | μΑ   |

| Sink Current Error                  | The temperature is 25°C                                     | -7   |        | +7    | %    |

| Temperature Drift                   |                                                             |      | -0.025 |       | %/°C |

| Over Temperature Moni               | tor                                                         |      |        |       |      |

| Overtemp Threshold                  | Generates interrupt or reset to MCU                         | 90   |        | 165   | °C   |

| Overtemp hysteresis                 |                                                             | -10  | -14    |       | °C   |

| Temperature Sensor                  |                                                             |      |        |       |      |

| Temperature detection range         | The MCU reads ADC data related to temperature detection     | -40  |        | 150   | °C   |

| Temperature detection<br>Accuracy   |                                                             | -10  |        | +10   | °C   |

| Active current                      |                                                             |      | 8      |       | μΑ   |

| Differential Amplifier (LS          | VFW measurement)                                            |      |        |       |      |

|                                  |                                                                                                                                                                                                     |             | T) (5           | B 4 A 3 C | 11117 |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|-----------|-------|

| PARAMETER                        | TEST CONDITION                                                                                                                                                                                      | MIN         | TYP             | MAX       | UNIT  |

| Input Voltage(Junction           | <4V @Gain=1/4                                                                                                                                                                                       | 0           |                 | 4         | V     |

| voltage range of LS lamp)        | >4V @Gain=1/8                                                                                                                                                                                       | 4           |                 | 8         | V     |

| Output Voltage Range             |                                                                                                                                                                                                     | 0           |                 | 1         | V     |

| Output Voltage<br>Relative Error |                                                                                                                                                                                                     |             |                 | 1         | %     |

| Gain                             | User configurable                                                                                                                                                                                   |             | 1/4 or 1/8      |           |       |

| Wake Up                          |                                                                                                                                                                                                     |             |                 |           |       |

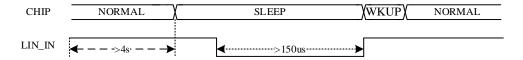

| TWAKEUP                          | LIN_IN/LIN_OUT, User configurable                                                                                                                                                                   | 30          | 150             | 200       | μs    |

| Wake Up Timer                    | Wakeup Time =TimerLoadCount/16kHz, TimerLoadCount = 0x0~0x1FFFFFF, the default value is 0x1FFFFFF                                                                                                   | 0           |                 | 2097152   | ms    |

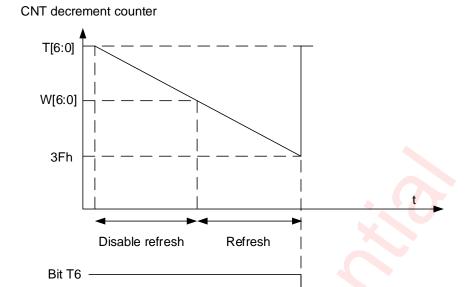

| ASIC Watchdog timer              |                                                                                                                                                                                                     |             |                 |           |       |

| Timeout                          | User configurable                                                                                                                                                                                   | 0.128       |                 | 16        | S     |

| SAR ADC                          | C.                                                                                                                                                                                                  |             |                 |           |       |

| Resolution                       |                                                                                                                                                                                                     |             | 12              |           | Bits  |

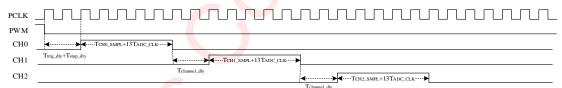

| Conversion Speed                 | 17 cycles per conversion (4 cycles for sampling and 13 cycles for conversion)                                                                                                                       |             |                 | 200       | ks/s  |

| ADC Clock                        | 16MHz RC clock d <mark>iv</mark> ided by 4                                                                                                                                                          |             |                 | 4         | MHz   |

| INL                              | Guaranteed by design                                                                                                                                                                                | -2          |                 | 2         | LSB   |

| DNL                              | Guaranteed by design                                                                                                                                                                                | -1          |                 | 1         | LSB   |

| Reference voltage <sup>1</sup>   | Post Calibration                                                                                                                                                                                    | 1.19        | 1.20            | 1.21      | V     |

| LIN(VBAT=8V~16V, VBI             | JS is the volta <mark>ge of LIN</mark> bus, VSUP is the                                                                                                                                             | chip's powe | r supply voltag | je)       |       |

| Supply Voltage                   | supply voltage range                                                                                                                                                                                | 6           | 13.5            | 18        | V     |

| IBUS_LIM                         | Current Limitation for Driver dominant state driver on VBUS = VBAT=16V                                                                                                                              | 40          |                 | 200       | mA    |

| Rslave                           | Lin Slave Pull-up                                                                                                                                                                                   | 20          | 30              | 60        | kΩ    |

| BUS_PAS_dom                      | Driver off, VBUS=0, VBAT=12V                                                                                                                                                                        | -1          |                 |           | mA    |

| IBUS_PAS_rec                     | Driver off, VBUS>VBAT<br>8V <vbat<16v, 8v<vbus<16v<="" td=""><td></td><td></td><td>20</td><td>μΑ</td></vbat<16v,>                                                                                   |             |                 | 20        | μΑ    |

| IBUS_no_GND                      | Control unit disconnected from<br>Ground, GND = VSUP<br>0V <vbus<16v, loss="" of<br="" vbat="12V,">local ground must not affect<br/>communication in the residual<br/>network. LIN 2.2A</vbus<16v,> | -1          |                 | +1        | mA    |

| IBUS_no_BAT                      | VBAT disconnected 0 <vbus<16v,< td=""><td></td><td></td><td>100</td><td>μA</td></vbus<16v,<>                                                                                                        |             |                 | 100       | μA    |

| PARAMETER                                            | TEST CONDITION                                                                                                                         | MIN            | TYP          | MAX            | UNIT |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|----------------|------|

|                                                      | VBAT=0V LIN 2.2A Node has to sustain the current that can flow under this condition. Bus must remain operational under this condition. |                |              |                |      |

| Device Bus Leakage<br>current VBAT<br>disconnected   | 0V <vbus<18v, vbat="VGND=0V&lt;br">J2602</vbus<18v,>                                                                                   | -23            |              | 23             | μA   |

| Device Bus Leakage<br>Current Ground<br>Disconnected | VBAT= VGND=12V, 0V <vbus<18v<br>J2602</vbus<18v<br>                                                                                    | -100           |              | 100            | μА   |

| BUS_VOL Transmitter dominant voltage                 | Load 500Ohms, driver open drain active                                                                                                 |                |              | 0.2*<br>VBUS   | V    |

| BUS_VOH Transmitter recessive voltage                | Driver open drain high impedance                                                                                                       | 0.8*<br>VBUS   |              |                | V    |

| C <sub>LIN</sub>                                     | LIN pin input capacitance                                                                                                              |                |              | 35             | pF   |

| VBUSrec                                              | Receiver recessive state                                                                                                               | 0.6*<br>VBUS   |              |                | V    |

| VBUSdom                                              | Receiver dominant state                                                                                                                | >              |              | 0.4*<br>VBUS   | V    |

| V <sub>hys</sub>                                     | Receiver hysteresis Vhys = VBUSrec -VBUSdom                                                                                            |                |              | 0.175*<br>VBUS | V    |

| VBUS_CNT                                             | Center point Receiver VBUS_CNT =( VBUSrec+VBUSdom)/2                                                                                   | 0.475*<br>VBUS | 0.5*<br>VBUS | 0.525*<br>VBUS | V    |

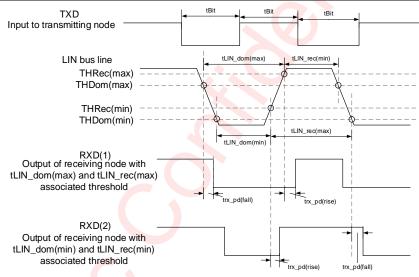

| Trx_pdr                                              | Rising edge propagation delay of receiver C <sub>RXD</sub> load 20pF (RX output of transceiver, internal node, access in test mode)    |                |              | 6              | μs   |

| Trx_pdf                                              | Falling edge propagation delay of receiver C <sub>RXD</sub> load 20pF (RX output of transceiver, internal node, access in test mode)   |                |              | 6              | μs   |

| Trx_sym                                              | symmetry of receiver propagation delay Trx_sym= Trx_pdf- Trx_pdr                                                                       | -2             |              | 2              | μs   |

| LIN Timing parameters                                | ·                                                                                                                                      |                |              |                |      |

| D1 Duty Cycle<br>(20kbits/s)                         | THRec(max) = 0.744 x VSUP;<br>THDom(max) = 0.581 x VSUP;<br>VSUP = 7.0V16V; tBit = 50µs;<br>D1 = tBus_rec(min) / (2 x tBit)            | 0.396          |              |                | -    |

| D2 Duty Cycle<br>(20kbits/s)                         | THRec(min) = 0.422 x VSUP;<br>THDom(min) = 0.284 x VSUP;<br>VSUP = 7.6V16V; tBit = 50μs;                                               |                |              | 0.581          | -    |

| PARAMETER                                             | TEST CONDITION                                                                                                              | MIN            | TYP | MAX            | UNIT |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|-----|----------------|------|

|                                                       | D2 = tBus_rec(max) / (2 x tBit)                                                                                             |                |     |                |      |

| D3 Duty Cycle<br>(10.4kbits/s)                        | THRec(max) = 0.778 x VSUP;<br>THDom(max) = 0.616 x VSUP;<br>VSUP = 7.0V16V; tBit = 96µs;<br>D3 = tBus_rec(min) / (2 x tBit) | 0.417          |     |                | -    |

| D4 Duty Cycle<br>(10.4kbits/s)                        | THRec(min) = 0.389 x VSUP;<br>THDom(min) = 0.251 x VSUP;<br>VSUP = 7.6V16V; tBit = 96µs;<br>D4 = tBus_rec(max) / (2 x tBit) |                | 6   | 0.59           | -    |

| t <sub>Bus_rec(max)</sub> - t <sub>Bus_dom(min)</sub> | Δt3, 10.4kbs operation, low speed mode, J2602                                                                               |                |     | 15.9           | μs   |

| t <sub>Bus_dom(max)</sub> - t <sub>Bus_rec(min)</sub> | Δt4, 10.4kbs operation, low speed mode, J2602                                                                               |                |     | 17.28          | μs   |

| GPIOs                                                 |                                                                                                                             | <b>~</b> (V)   |     |                |      |

| GPIO V <sub>I</sub> L                                 | Input Low Voltage                                                                                                           |                |     | 0.3*<br>VDD3V3 | V    |

| GPIO V <sub>IH</sub>                                  | Input High Voltage                                                                                                          | 0.7*<br>VDD3V3 |     |                | V    |

| GPIO IoL                                              | Max load current with output voltage=VOL                                                                                    | ,              |     | 10             | mA   |

| GPIO I <sub>OH</sub> <sup>2</sup>                     | Max load current with output voltage=VOLH                                                                                   |                |     | 10             | mA   |

| GPIO V <sub>OL</sub>                                  | Output Low Voltage                                                                                                          |                |     | 0.4            | V    |

| GPIO V <sub>OH</sub>                                  | Output High Voltage                                                                                                         | 2.4            |     |                | V    |

| GPIO P∪                                               | Pull Up Resistance                                                                                                          |                | 50  |                | kΩ   |

| GPIO P <sub>D</sub>                                   | Pull Down Resistance                                                                                                        |                | 50  |                | kΩ   |

| GPIOMs                                                | *.                                                                                                                          |                |     |                |      |

| GPIOM V <sub>IL</sub>                                 | Input Low Voltage                                                                                                           |                |     | 0.3*<br>VDD3V3 | V    |

| GPIOM V <sub>IH</sub>                                 | Input High Voltage                                                                                                          | 0.7*<br>VDD3V3 |     |                | V    |

| GPIOM I <sub>OL</sub>                                 | Max load current with output voltage=VOL                                                                                    |                |     | 5              | mA   |

| GPIOM I <sub>OH</sub> <sup>2</sup>                    | Max load current with output voltage=VOLH                                                                                   |                |     | 5              | mA   |

| GPIOM Vol                                             | Output Low Voltage                                                                                                          |                |     | 0.4            | V    |

| GPIOM Voh                                             | Output High Voltage                                                                                                         | 2.4            |     |                | V    |

| GPIOM Pu                                              | Pull Up Resistance                                                                                                          |                | 20  |                | kΩ   |

| GPIOM PD                                              | Pull Down Resistance                                                                                                        |                | 20  |                | kΩ   |

# AW32F020

Aug. 2025 V1.0

| PARAMETER           | TEST CONDITION | MIN    | TYP | MAX    | UNIT |

|---------------------|----------------|--------|-----|--------|------|

| SWCLK, SWDIO        |                |        |     |        |      |

| SWD V <sub>IL</sub> |                |        |     | 0.3*   | V    |

|                     |                |        |     | VDD3V3 |      |

| SWD V <sub>IH</sub> |                | 0.7*   |     |        | V    |

| SVVD VIH            |                | VDD3V3 |     |        |      |

| SWD V <sub>OL</sub> |                |        |     | 0.4    | V    |

| SWD V <sub>OH</sub> |                | 2.4    |     |        | V    |

| SWD Pu              |                |        | 20  |        | kΩ   |

Note1: Minimum and/or maximum limit is guaranteed by design and by statistical analysis of device characterization data. The specification is not guaranteed by production testing.

Note2: The sum of max load current of all GPIO/GPIOM and VCC3V3\_SW is 35mA.

17

# **TYPICAL CHARACTERISTICS**

# **CURRENT CONSUMPTION**

| Mode   | Conditions                                                                                                                                                                                                                 | Min | Тур | Max | Unit |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Normal | Ta=85°C, VBAT=18V, RCO=16MHz, full functionality: MCU running, no flash write, LS OFF, ADC ON, VBAT and TEMP monitor ON, WDT ON.                                                                                           |     |     | 10  | mA   |

| Sleep  | Main regulator (3.3V) ON, Load dump protection active. Ta=85degC max, VBAT=13.5V Overvoltage/Undervoltage detection, PWM, LS driver, Temp_sensor and ADC are OFF except one LIN RX on and GPIO toggling and wake up timer. | 15  | 35  | 60  | μА   |

Figure 5 LIN timing

Figure 6 LIN test circuit

# SYSTEM AND FLASH OVERVIEW

This chapter describes how to power on, power off, initialize and fine-tune the system, and enter and exit the low-power mode.

# **POWER-ON**

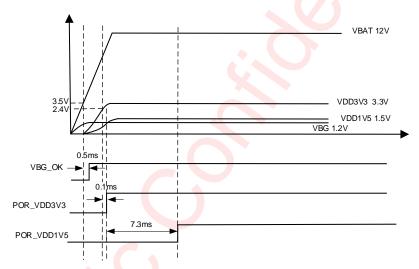

The car battery is powered by VBAT, and there are multiple LDOs inside the chip to establish the on-chip power system:

LDO3V3: Input: 13.5V, Output: 3.3VLDO1V5: Input: 3V, Output: 1.5V

After the power supply is connected to the VBAT pin (the peripheral circuit of AW32F020QNR-Q1 has been confirmed to be intact), the voltage on the chip power pin VBAT pin meets the working voltage range, and the system will start to work.

The following figure shows the power-on timing relationship of AW32F020QNR-Q1 (VBAT, LDO, GPIO, LIN, etc.):

Figure 7 AW32F020QNR-Q1 Power on Timing

After rising from POR\_VDD1V5, the hardware initialization time is 2.1ms. Considering the hardware initialization time, it is about 10ms from the start of power on to the chip being able to work normally.

# **POWER-DOWN**

When VDD 3V3 or VBAT is below the preset voltage threshold, the whole chip will be reset immediately.

# **MEMORY**

AW32F020QNR-Q1 has a built-in 16KB SRAM, which can support byte (8 bits), half-word (16 bits), or word (32 bits) read and write access. The built-in FLASH size is 64KB, supports read, write, erase operations, and supports access with 32-bit words. FLASH is used to save the chip execution code, including initialization procedures and various detection, judgment, processing procedures.

- 64KB embedded FLASH for storing programs and data

- 6KB NVR area for storing user configuration information

# **MEMORY MAPPINGS**

awinic

| Address                               | Interface        | Description                                 |

|---------------------------------------|------------------|---------------------------------------------|

| 0x00000000 – 0x0000FFFF               | FLASH            | 64Kbytes of Flash Memory, user programmable |

| 0x00010000 - 0x000117FF               | NVR              | 6KB                                         |

| 0x00012000 – 0x1FFFFFF                | NA               | -                                           |

| 0x20000000 - 0x20003FFF               | SRAM             | 16KB SRAM                                   |

| 0x20004000 - 0x3FFFFFF                | NA               | -                                           |

| 0x40004000 - 0x400040FF               | WDT              | Watchdog timer                              |

| 0x40004100 - 0x400041FF               | TIMER1           | Basic timer 1                               |

| 0x40004200 - 0x400042FF               | TIMER2           | Basic purpose timer 2                       |

| 0x40004300 - 0x400043FF               | TIMER3           | General purpose timer 3                     |

| 0x40004400 - 0x400044FF               | RCCM             | Timer, WDT Clock Reset Controller           |

| 0x40004500 - 0x400045FF               | FMC              | FLASH controller                            |

| 0x40004600 - 0x400046FF               | SYSCTRL          | <b>(</b> )                                  |

| 0x40004700 - 0x400047FF               | NA               |                                             |

| 0x40004800 - 0x400048FF               | GPIOM            | MCU GPIO bit control and configuration      |

| 0x40004900 - 0x400049FF               | SPI              | SPI Register                                |

| 0x40004A00 - 0x40004AFF               | I <sup>2</sup> C | I <sup>2</sup> C Register                   |

| 0x40004B00 - 0x40004BFF               | UART             | UART Register                               |

| 0x40004C00 - 0x40004CFF               | NA               |                                             |

| 0x40004D00 – 0x4FFFFFF                | NA               | ,                                           |

| 0x50000000 - 0x500000FF               | RCC              | Clock & Reset Generator                     |

| 0x50000100 - 0x500001FF               | PMU              | Power Management Unit                       |

| 0x50000200 - 0x500002FF               | NA               | -                                           |

| 0x50000300 - 0x500003FF               | WWDG             | Window Watchdog Register                    |

| 0x50000400 - 0x500004FF               | LS_CTRL          | LS Controllers                              |

| 0x50000500 - 0x500005FF               | LINS             | LIN slave control and PHY registers         |

| 0x50000600 - 0x500006FF               | LINM             | LIN master PHY register                     |

| 0x50000700 - 0x500007FF               | ADC_CTRL         | ADC controller                              |

| 0x50000800 - 0x500 <mark>008FF</mark> | AFIO             | Alternate function                          |

| 0x50000900 - 0x500009FF               | SYSCTRL          | System configuration and retention memory   |

| 0x50000A00 - 0x50000AFF               | GPIO             | GPIO bit control and configuration          |

| 0x50000E00 - 0x50000EFF               | WAKEUP TIMER     | Wake up timer                               |

# **DETAILED FUNCTIONAL DESCRIPTION**

# **CORE PERFORMANCE**

AW32F020QNR-Q1 integrates a 32-bit CPU core. The platform provides excellent computing performance and efficient interrupt system, while the peripheral devices use less pins and lower power consumption.

A nested vector interrupt controller is built in. The interrupt controller can handle up to 32 maskable interrupt channels and supports four different interrupt priorities.

#### INTERRUPT AND EXCEPTION VECTORS

The vector table of AW32F020QNR-Q1 is as follows.

| Location | Priority | Priority type  | Abbreviations            |

|----------|----------|----------------|--------------------------|

| -        | -3       | Fixed          | Reset_Handler            |

| -        | -2       | Fixed          | NMI_Handler              |

| -        | -1       | Fixed          | HardFault_Handler        |

| -        | 0        | Configurable ( | MemManage_Handler        |

| -        | 1        | Configurable   | BusFault_Handler         |

|          | 2        | Configurable   | UsageFault_Handler       |

| -        | 3        | Configurable   | SVC_Handler              |

|          | 4        | Configurable   | DebugMon_Handler         |

| -        | 5        | Configurable   | PendSV_Handler           |

| -        | 6        | Configurable   | SysTick_Handler          |

| 0        | 7        | Configurable   | WDT_Handler              |

| 1        | 8        | Configurable   | Timer1_Handler           |

| 2        | 9        | Configurable   | Timer2_Handler           |

| 3        | 10       | Configurable   | Timer3Handler            |

| 8        | 15       | Configurable   | GPIOM_Handler            |

| 9        | 16       | Configurable   | SPI_Handler              |

| 10       | 17       | Configurable   | I <sup>2</sup> C_Handler |

| 11       | 18       | Configurable   | UART_Handler             |

| 16       | 23       | Configurable   | LINS_WU_Handler          |

| 17       | 24       | Configurable   | LINS_PHY_Handler         |

| 18       | 25       | Configurable   | TIMER_WU_Handler         |

| 19       | 26       | Configurable   | BOR_Handler              |

| 20       | 27       | Configurable   | WWDG_Handler             |

| 21       | 28       | Configurable   | UV_Handler               |

| 22       | 29       | Configurable   | OV_Handler               |

| 23       | 30       | Configurable   | LINS_Handler             |

| 24       | 31       | Configurable   | ADC_Handler              |

| 27       | 34       | Configurable   | GPIO_Handler             |

| 29       | 36       | Configurable   | OVTEMP_Handler           |

|          |          |                |                          |

# **FLASH CTRL**

#### **OVERVIEW**

AW32F020QNR-Q1 is equipped with a built-in 64KB FLASH memory, which serves as storage for the application program. Upon powering up the chip, the CPU fetches instructions from the FLASH to execute the application program.

# **FEATURES**

- 64KB FLASH main storage area and 6KB user NVR area, 512 bytes per sector

- Support FLASH writing in word

- Support FLASH sector erase, FLASH chip erase

- Support high-speed access to the FLASH storage area using the AHB bus

- Support code protect

# **FUNCTIONAL DESCRIPTION**

# **FLASH Structure**

| FLASH area                | Name             | FLASH Adress                             | Size (byte) |

|---------------------------|------------------|------------------------------------------|-------------|

|                           | Sector 0         | 0x000 <mark>0 0000 - 0x</mark> 0000 01FF | 0.5 Kbyte   |

|                           | Sector 1         | 0x0000 0200 - 0x0000 03FF                | 0.5 Kbyte   |

|                           | Sector 2         | 0x <mark>0000</mark> 0400 - 0x0000 05FF  | 0.5 Kbyte   |

|                           | Sector 3         | 0x00 <mark>0</mark> 0 0600 - 0x0000 07FF | 0.5 Kbyte   |

| Main FLASH<br>Memory(64K) |                  |                                          |             |

|                           | Sector 124       | 0x0000 F800 - 0x0000 F9FF                | 0.5 Kbyte   |

|                           | Sector 125       | 0x0000 FA00 - 0x0000 FBFF                | 0.5 Kbyte   |

|                           | Sector 126       | 0x0000 FC00 - 0x0000 FDFF                | 0.5 Kbyte   |

| 4                         | Sector 127       | 0x0000 FE00 - 0x0000 FFFF                | 0.5 Kbyte   |

|                           | Usr nvr Sector0  | 0x0001 0000 - 0x0001 01FF                | 0.5 Kbyte   |

|                           | Usr nvr Sector1  | 0x0001 0200 - 0x0001 03FF                | 0.5 Kbyte   |

|                           | Usr nvr Sector2  | 0x0001 0400 - 0x0001 05FF                | 0.5 Kbyte   |

|                           | Usr nvr Sector3  | 0x0001 0600 - 0x0001 07FF                | 0.5 Kbyte   |

| NVR block                 |                  |                                          |             |

| (6K)                      |                  |                                          |             |

|                           | •                |                                          |             |

|                           | Usr nvr Sector9  | 0x0001 1200 - 0x0001 11FF                | 0.5 Kbyte   |

|                           | Usr nvr Sector10 | 0x0001 1400 - 0x0001 13FF                | 0.5 Kbyte   |

|                           | Usr nvr Sector11 | 0x0001 1600 - 0x0001 17FF                | 0.5 Kbyte   |

## **FLASH Read Protection**

When the chip is powered on or the system is reset, the debug interface is disabled during the instruction

period of the first 8192 cycles of CPU execution.

Write 0x91827364 to the register FLS\_CODE\_PROT to enable FLASH read protection and disable the debug interface.

Note: If the read protection function is turned on within 8192 instruction cycles after the power reset or system reset of the chip, the chip will not be connected through the debug interface later.

#### **FLASH Power down Protection**

In order to prevent damage to FLASH caused by unexpected power down in the process of FLASH erasing and writing, FLASH power down protection function can be enabled before FLASH erasing and writing operations. Here's how:

- Step 1: Start the unexpected power down protection circuit (write 0x1 to register FLS\_BOR\_CFG);

- Step 2: Wait for 100µs;

- Step 3: Enable the unexpected power down protection function (write 0x3 to register FLS\_BOR\_CFG);

### **FLASH Erase Initialization**

FLASH erase and write operations have different timing requirements under different system clock frequencies. The timing parameters of FLASH erase and write operations are configured as follows:

| Register  | Pro   | ogrammin | g    | Sector Erase |        |        | Chip Erase |         |         |

|-----------|-------|----------|------|--------------|--------|--------|------------|---------|---------|

| rtogiotor | 16M   | 8M       | 4M   | 16M          | 8M     | 4M     | 16M        | 8M      | 4M      |

| T_NVS     | 0x190 | 0xC8     | 0x64 | 0x190        | 0xC8   | 0x64   | 0x5A0      | 0x2D0   | 0x168   |

| T_PGS     | 0x3C0 | 0x1E0    | 0xF0 | 0x3C0        | 0x1E0  | 0xF0   | 0x3C0      | 0x1E0   | 0xF0    |

| T_PROG    | 0x5C  | 0x2E     | 0x17 | 0x5C         | 0x2E   | 0x17   | 0x5C       | 0x2E    | 0x17    |

| T_RCV     | 0x3C0 | 0x1E0    | 0xF0 | 0x3C0        | 0x1E0  | 0xF0   | 0xDC0      | 0x6E0   | 0x370   |

| T_RW      | 0xC   | 0x6      | 0x3  | 0xC          | 0x6    | 0x3    | 0xC0       | 0x60    | 0x30    |

| T_ERASE   |       |          |      | 0x9600       | 0x4B00 | 0x2580 | 0x84D00    | 0x42680 | 0x21340 |

| T_WAKEUP  | 0x192 | 0xC8     | 0x64 | 0x192        | 0xC8   | 0x64   | 0x192      | 0xC8    | 0x64    |

| T_ADSH    | 0xC   | 0x6      | 0x3  | 0xC          | 0x6    | 0x3    | 0xC        | 0x6     | 0x3     |

#### **FLASH Sector Erase**

- 1) Configure the timing parameters of the FLASH sector erase operation based on the system clock frequency, and reference to the recommended parameters in FLASH erase initialization.

- 2) Configure the ISP ADR register: writing the address of the FLASH sector to be erased.

- 3) Configure the ISP\_CMD register: setting the ISP\_CMD bit field with the erase instruction. If the target FLASH address is in NVR region, set ISP\_NVR bit field to 1, otherwise, set it to 0. Set ISP\_CHIP bit field to 0.

- 4) Configure the ISP\_GO register: setting the ISP\_GO bit field to 1 to initiate sector erase operation. When this bit is cleared, indicating completion of sector erase operation.

# **FLASH Chip Erase**

- 1) Configure the timing parameters of the FLASH full-chip erase operation based on the system clock frequency, and reference to the recommended parameters in the FLASH erase initialization.

- 2) Configure the ISP\_CMD register: writing the erase instruction to the ISP\_CMD bit field; set ISP\_NVR bit field to 0; set ISP\_CHIP bit field to 1.

- 3) Configure the ISP\_GO register: writing 1 to the ISP\_GO bit field to start the full-chip erase operation; When this bit is cleared, indicating that the full-chip erase operation is complete.

# **FLASH Write**

Users can write data to the address by accessing it directly.

# **FLASH Read**

Users can read FLASH data at a specified address through direct address access.

# **REGISTER LIST**

# **Register Mapping**

FLASH\_CTRL\_BASE: 0x40004500

| Offset | Register Name | Description                    | Reset Value |

|--------|---------------|--------------------------------|-------------|

| 0x00   | ISP_CR        | ISP Control Register           | 0x100       |

| 0x04   | ISP_ADDR      | ISP Address Register           | 0x0         |

| 0x10   | ISP_CMD       | ISP Command Register           | 0x20        |

| 0x14   | ISP_GO        | ISP Go Register                | 0x0         |

| 0x20   | T_NVS         | T_NVS Register                 | 0x190       |

| 0x24   | T_PGS         | T_PGS Register                 | 0x3C0       |

| 0x28   | T_PROG        | T_PROG Register                | 0x5C        |

| 0x2C   | T_RCV         | T_RCV Register                 | 0x3C0       |

| 0x30   | T_RW          | T_RW Register                  | 0xC         |

| 0x34   | T_ERASE       | T_ERASE Register               | 0x9600      |

| 0x38   | T_WAKEUP      | T_WAKEUP Register              | 0x192       |

| 0x40   | T_ADSH        | T_ADSH Register                | 0xC         |

| 0x48   | FLS_CODE_PROT | FLASH Code Protection Register | 0x0         |

| 0x4C   | BOR_CFG       | FLASH BOR Configue Register    | 0x0         |

| 0x54   | BOR_STATE     | BOR State Register             | 0x0         |

# **Register Detailed Description**

RO: Read only, W: Write only, RW: Read/Write

| ISP_CR: Address(0x000) |              |     |                                                                                    |         |  |  |

|------------------------|--------------|-----|------------------------------------------------------------------------------------|---------|--|--|

| Bit                    | Symbol       | R/W | Description                                                                        | Default |  |  |

| 31:9                   | Reserved     | RO  | Not used                                                                           | 0       |  |  |

| 8                      | BYPASS_WR_FF | RW  | O: Writing FF to flash will not be skipped  1: Writing FF to flash will be skipped | 1       |  |  |

| 7:0                    | Reserved     | RO  | Not used                                                                           | 0       |  |  |

| ISP_ADR: Address(0x004) |          |     |                                                                       |         |  |  |

|-------------------------|----------|-----|-----------------------------------------------------------------------|---------|--|--|

| Bit                     | Symbol   | R/W | Description                                                           | Default |  |  |

| 31:16                   | Reserved | RO  | Not used                                                              | 0       |  |  |

| 15:0                    | ISP_ADR  | RW  | Indicates the destination address of the ISP operation: 0x0000~0xFFFF | 0       |  |  |

| ISP_CMI | ISP_CMD: Address(0x010) |     |                                                                         |         |  |  |  |

|---------|-------------------------|-----|-------------------------------------------------------------------------|---------|--|--|--|

| Bit     | Symbol                  | R/W | Description                                                             | Default |  |  |  |

| 31:9    | Reserved                | RO  | Not used                                                                | 0       |  |  |  |

| 8       | READONLY                | RW  | READONLY=1 to prohibit programming and erase operations.                | 0       |  |  |  |

| 7:6     | Reserved                | RO  | Not used                                                                | 0       |  |  |  |

| 5       | ISP_NVR                 | RW  | NVR sector selection.  0: Select FLASH main area;  1: Select NVR area . | 0       |  |  |  |

| 4       | ISP_CHIP                | RW  | Chip selection signal.  0: sector erase;  1: chip erase.                | 0       |  |  |  |

| 3:0     | ISP_CMD                 | RW  | ISP command. 0101: Erase; Others: Reserved.                             | 0       |  |  |  |

| ISP_GO: Address(0x014) |          |     |                                                                                                                                                                                                   |         |

|------------------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit                    | Symbol   | R/W | Description                                                                                                                                                                                       | Default |

| 31:1                   | Reserved | RO  | Not used                                                                                                                                                                                          | 0       |

| 0                      | ISP_GO   | RW  | ISP operation start signal.(software write 1, hardware reset)  0: ISP operation completed, when ISP_GO is zero, software can be allowed to configure registers;  1: ISP operation is in progress. | 0       |

| T_NVS: A | T_NVS: Address(0x020) |     |                                                                                                                                                                                                                                                                                                                      |         |  |  |  |  |

|----------|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| Bit      | Symbol                | R/W | Description                                                                                                                                                                                                                                                                                                          | Default |  |  |  |  |

| 31:11    | Reserved              | RO  | Not used                                                                                                                                                                                                                                                                                                             | 0       |  |  |  |  |

| 10:0     | T_NVS                 | RW  | PROG/ERASE/CEb/NVR/Address set up time to Web.(unit: system clock period) Program: Min=20µs; 16MHz: T_NVS=0x190; 8MHz: T_NVS=0xC8; 4MHz: T_NVS=0x64. Sector erase: Min=20µs; 16MHz: T_NVS=0x190; 8MHz: T_NVS=0xC8; 4MHz: T_NVS=0x64. Chip Erase: Min=80µs; 16MHz: T_NVS=0x5A0; 8MHz: T_NVS=0x2D0; 4MHz: T_NVS=0x168. | 0x190   |  |  |  |  |

| T_PGS: Address(0x024) |          |     |             |         |  |  |

|-----------------------|----------|-----|-------------|---------|--|--|

| Bit                   | Symbol   | R/W | Description | Default |  |  |

| 31:11                 | Reserved | RO  | Not used    | 0       |  |  |

25

| 10:0 | T_PGS | RW | Web low level to PROG2 high level to set up tilme.(unit: system clock period) T_PGS: Min=50 µs ,Max=70 µs. | 0x3C0 |

|------|-------|----|------------------------------------------------------------------------------------------------------------|-------|

|      |       |    | 16MHz: T_PGS=0x3C0; 8MHz: T_PGS=0x1E0; 4MHz: T_PGS=0xF0.                                                   |       |

| T_PROG: Address(0x028) |          |         |                                                                                                                                     |      |  |

|------------------------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Bit                    | Symbol   | Default |                                                                                                                                     |      |  |

| 31:7                   | Reserved | RO      | Not used                                                                                                                            | 0    |  |

| 6:0                    | T_PROG   | RW      | Byte program time.(unit: sysytem clock period) T_PROG Min=5µs, max=6.5µs. 16MHz: T_PROG=0x5C; 8MHz: T_PROG=0x2E; 4MHz: T_PROG=0x17. | 0x5C |  |

| T_RCV: Add | dress(0x02C) |     |                                                                                                                                                                                                                                                                                               |         |  |

|------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit        | Symbol       | R/W | Description                                                                                                                                                                                                                                                                                   | Default |  |

| 31:13      | Reserved     | RO  | Not used                                                                                                                                                                                                                                                                                      | 0       |  |

| 12:0       | T_RCV        | RW  | program/erase reset time(unit: sysytem period) Program: Min=50µs; 16MHz: T_RCV=0x3C0; 8MHz: T_RCV=0x1E0; 4MHz: T_RCV=0xF0. Sector erase: Min=50µs; 16MHz: T_RCV=0x3C0; 8MHz: T_RCV=0x1E0; 4MHz: T_RCV=0xF0. Chip Erase: Min=200 µs; 16MHz: T_RCV=0xDC0; 8MHz: T_RCV=0x6E0; 4MHz: T_RCV=0x370. | 0x3C0   |  |

| T_RW: Ad | T_RW: Address(0x030) |                 |                                                                                                                                                                                                                                                                                                        |         |  |  |

|----------|----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Bit      | Symbol               | R/W Description |                                                                                                                                                                                                                                                                                                        | Default |  |  |

| 31:8     | Reserved             | RO              | Not used                                                                                                                                                                                                                                                                                               | 0       |  |  |

| 7:0      | T_RW                 | RW              | PROG/ERASE signal low level to next operation delay time.(unit: sysytem time) Program: Min=0.5µs; 16MHz: T_RW=0xC; 8MHz: T_RW=0x6; 4MHz: T_RW=0x3. Sector erase: Min=0.5µs; 16MHz: T_RW=0xC; 8MHz: T_RW=0x6; 4MHz: T_RW=0x3. Chip Erase: Min=10µs; 16MHz: T_RW=0xC0; 8MHz: T_RW=0x60; 4MHz: T_RW=0x30. | 0xC     |  |  |

| T_ERASE: | T_ERASE: Address(0x034) |                        |                                                                                                                                                                                                                                                      |         |  |

|----------|-------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit      | Symbol                  | Symbol R/W Description |                                                                                                                                                                                                                                                      | Default |  |

| 31:20    | Reserved                | RO                     | Not used                                                                                                                                                                                                                                             | 0       |  |

| 19:0     | T_ERASE                 | RW                     | ISP erase time.(unit: sysytem clock period) Sector erase: min=2ms, max=3ms; 16MHz: T_ERASE=0x9600; 8MHz: T_ERASE=0x4B00; 4MHz: T_ERASE=0x2580. Chip erase: min=30ms, max=40ms; 16MHz: T_ERASE=0x84D00; 8MHz: T_ERASE=0x42680; 4MHz: T_ERASE=0x21340. | 0x9600  |  |

| T_WAKE | JP: Address(0x038) |     |                                                                                                                                                                         |         |

|--------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Bit    | Symbol             | R/W | Description                                                                                                                                                             | Default |

| 31:9   | Reserved           | RO  | Not used                                                                                                                                                                | 0       |

| 8:0    | T_WAKEUP           | RW  | Flash wakeup time(unit: sysytem period)  FWUP=1: T_WAKEUP min = 10µs;  FWUP=0: T_WAKEUP min = 20µs;  16MHz: T_WAKEUP=0x192;  8MHz: T_WAKEUP=0xC8;  4MHz: T_WAKEUP=0x64. | 0x192   |

| T_ADSH: Address(0x040) |          |                        |                                                                                                                             |     |  |

|------------------------|----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|--|

| Bit                    | Symbol   | Symbol R/W Description |                                                                                                                             |     |  |

| 31:5                   | Reserved | RO                     | Not used                                                                                                                    | 0   |  |

| 4:0                    | T_ADSH   | RW                     | BYTE[3:0]/Address/data setup/hold timing set. T_ADS\T_ADH: Min=0.5µs; 16MHz:T_ADSH=0xC; 8MHz: T_ADSH=0x6; 4MHz: T_ADSH=0x3. | 0xC |  |

| FLS_C | FLS_CODE_PROT: Address(0x048) |     |                                                                                                                                                                  |         |  |  |  |

|-------|-------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

| Bit   | Symbol                        | R/W | Description                                                                                                                                                      | Default |  |  |  |

| 31:0  | FLS_CODE_PROT                 | RW  | Write 0x91827364 to enable flash read protection function.  0: The flash read protection function is enabled;  1: The flash read protection function is disabled | 0       |  |  |  |

| BOR_CF | BOR_CFG: Address(0x04C) |     |                                                                                                                                                           |         |  |

|--------|-------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Bit    | Symbol                  | R/W | Description                                                                                                                                               | Default |  |

| 31:2   | Reserved                | RO  | Not used                                                                                                                                                  | 0       |  |

| 1      | FBOR_BOR_VALID          | RW  | This register is valid when FBOR_EN is set to 1.  0: Disable sudden power failure protection function  1: Enable sudden power failure protection function | 0       |  |

| 0      | FBOR_EN                 | RW  | Disable power down protection circuit     Enable power down protection circuit                                                                            | 0       |  |

| BOR_STATE | BOR_STATE: Address(0x054) |                        |                                                                                                                                 |   |  |  |

|-----------|---------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------|---|--|--|

| Bit       | Symbol                    | Symbol R/W Description |                                                                                                                                 |   |  |  |

| 31:1      | Reserved                  | RO                     | Not used                                                                                                                        | 0 |  |  |

| 0         | FBOR_BOR                  | RW                     | Unexpected power failure indicator, this bit is written 1 to clear 0 0: No unexpected power failure 1: Unexpected power failure | 0 |  |  |

# **TIMER1/TIMER2**

# **OVERVIEW**

TIMER1 and TIMER2 both contain a 32-bit counter that can be used as basic timers to provide timing functionality to the system.

# **FEATURES**

- 32-bit counter, working in the system clock domain.

- Support interrupt control functions, including interrupt generation, interrupt clearing, and interrupt masking.

- When the timer is working, TimerLoadCount changes. It will only be updated by the timer when it reaches 0 or when it is restarted. Otherwise, the timer will continue to decrease until it reaches 0 before updating TimerLoadCount.

#### **FUNCTIONAL DESCRIPTION**

1) Start the TIMER Clock

The enable and disable of TIMER1 and TIMER2 clocks can be achieved through RCCM.CLKENR register.

2) Configure TIMER loading value

The TIMER reload value can be configured through the TIMERx. TimerLoaderCount register.

3) Configure TIMER interrupt

TIMER interrupts are enabled and masked by the TIMERx. TimerControlReg register.

4) Start TIMER interrupt

Enable the TIMER global interrupt and configure the appropriate interrupt priority according to the application.

5) Start the TIMER

TIMER enable and disable can be configured by the TIMERx.TimerControlReg register.

#### 6) TIMER interrupt generating

When the TIMER is enabled, the counter starts counting down from the value configured in the TIMERx.TimerLoaderCount register. When the count is decreased to 0, the TIMER interrupt is generated, and the counter value is restored to the value configured in the TIMERx.TimerLoaderCount register, and the counting down starts again.

## 7) TIMER interrupt clearing

After the TIMER interrupt is generated, the register TIMERx. TimerEOI needs to be written to clear the TIMER interrupt state.

# 8) Reconfigure the TIMER count value