## Low Quiescent, High Efficiency 1.5 A Buck-Boost Converter with I<sup>2</sup>C Interface

#### **Features**

- Buck, Buck-Boost and Boost Operation with Seamless Mode Transition

- 2.2V to 5.5V Input Supply Voltage Range

- 2.025V to 5.2V Output Voltage Range with Digitally Programmable (25mV/steps)

- 2.8uA Low Quiescent Current

- 0.3uA Shutdown Current

- Excellent Load Transient Response

- Allows Dynamically-Voltage-Scaling Control

- Automatic PFM Mode and Forced PWM Mode Selection

- Up to 1MHz I<sup>2</sup>C Interface(I<sup>2</sup>C supports 1.2V I/O)

- Output Voltage Selection (VSEL=H, VOUT=3.5V Default; VSEL=L, VOUT=3.3V Default)

- Maximum Continuous Output Current:

Up to 0.8A for VIN ≥ 2.2V, VOUT = 3.5V

Up to 1A for VIN ≥ 2.5V, VOUT = 3.5V

Up to 1.5A for VIN ≥ 3.3V, VOUT = 3.5V

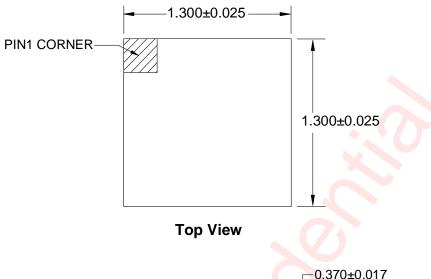

- WLCSP 1.3X1.3-9B Package

## **Applications**

- Wearable Devices

- Portable Devices

- TWS Earbud Chargers

- Optical Heart Rate Monitor LED Bias

- Battery Powerd Systems

- Smartphones

### **General Description**

The AWP37701Z is a high-efficiency, single inductor, advanced COT synchronous Buck-Boost converter with 2.2V to 5.5V wide input voltage range and well regulate to the digitally programmable output voltage from 2.025V to 5.2V. Which is suitable for wide input supply range applications, regardless of input voltage is lower, higher than or even equal to the output voltage. The COT control architecture features outstanding line/load transient response, seamless transition between buck and boost modes, provides stable operation with small ceramic output capacitors and without complicated external compensation.

The AWP37701Z features I<sup>2</sup>C interface, which allows programmable output voltage, soft-start slew-rate adjusted and device status monitoring. The target output voltage can also be switched through external VSEL pin to perform dynamically-voltage-scaling (DVS), and the ramp-up slew-rate and ramp mode of DVS can also be set by setting the related registers.

The AWP37701Z has internal soft start module to limits the inrush current. Full protection features include over current protection(OCP), short circuit protection(SCP), over voltage protection(OVP), under voltage protection(UVP) and over temperature protection(OTP). The AWP37701Z is available in WLCSP 1.3X1.3-9B package.

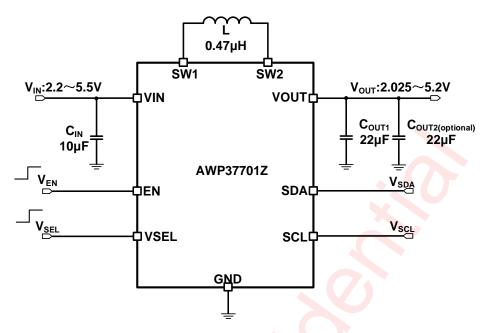

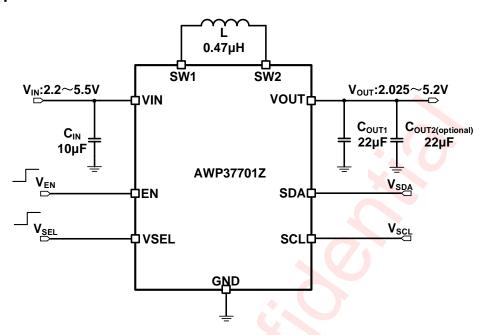

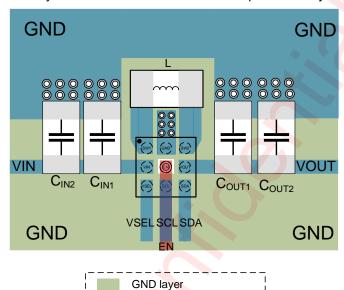

## **Typical Application Circuit**

Figure 1 AWP37701Z Typical Application Circuit

NOTE: When the output current is ≤1A, a 22µF COUT is recommended. When the output current is >1A, 2 × 22µF COUT capacitors are recommended. The recommended maximum output current should not exceed 1.5A.

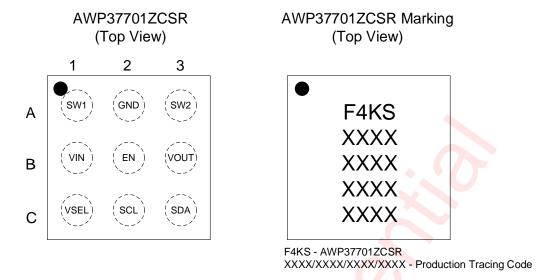

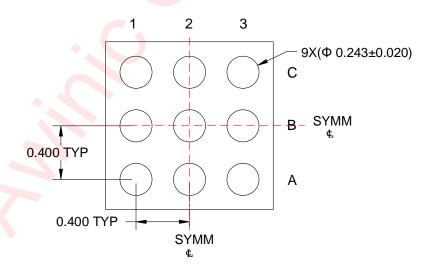

## **Pin Configuration And Top Mark**

Figure 2 Pin Configuration and Top Mark

#### **Pin Definition**

| No. | NAME | DESCRIPTION                                                                                                                                   |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | SW1  | Switching node 1. Connect to the inductor.                                                                                                    |

| A2  | GND  | Ground. All signals are referenced to this pin.                                                                                               |

| А3  | SW2  | Switching node 2. Connect to the inductor.                                                                                                    |

| B1  | VIN  | Power input.                                                                                                                                  |

| B2  | EN   | Enable control input. A logic-high enables the converter; a logic-low forces the device into shutdown mode.                                   |

| В3  | VOUT | Power output.                                                                                                                                 |

| C1  | VSEL | Voltage select pin. When this pin is logic low, VOUT is set by the VOUT1 register; This pin is logic high, VOUT is set by the VOUT2 register. |

| C2  | SCL  | I <sup>2</sup> C serial interface clock.                                                                                                      |

| C3  | SDA  | I <sup>2</sup> C serial interface data.                                                                                                       |

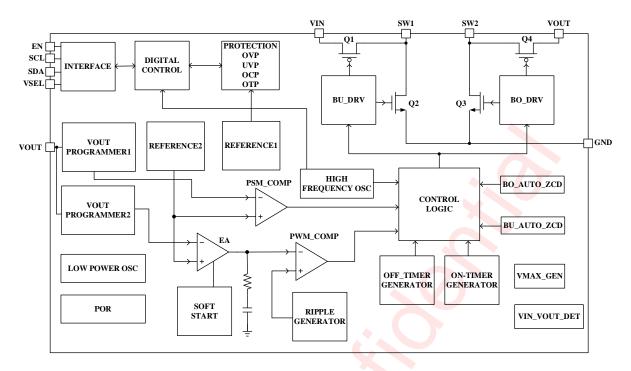

## **Functional Block Diagram**

Figure 3 Functional Block Diagram

## **Ordering Information**

| Part Number  | Temperatu<br>re | Package          | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery Form                |

|--------------|-----------------|------------------|---------|----------------------------------|------------------------------|------------------------------|

| AWP37701ZCSR | -40°C∼85°C      | WLCSP 1.3X1.3-9B | F4KS    | MSL1                             | ROHS+HF                      | 4500 units/<br>Tape and Reel |

## Absolute Maximum Ratings(NOTE1)

| PARAMETERS                                                     | RANGE          |  |  |

|----------------------------------------------------------------|----------------|--|--|

| Supply voltage range VIN                                       | -0.3V to 6V    |  |  |

| Power output voltage range VOUT                                | -0.3V to 6V    |  |  |

| SW1、SW2                                                        | -0.3V to 6.5V  |  |  |

| IO voltage range EN、VSEL、SDA、SCL                               | -0.3V to 6V    |  |  |

| Junction-to-ambient thermal resistance θ <sub>JA</sub> (NOTE2) | 100.3°C /W     |  |  |

| Maximum operating junction temperature T <sub>JMAX</sub>       | 150°C          |  |  |

| Storage temperature T <sub>STG</sub>                           | -65°C to 150°C |  |  |

| Lead temperature (soldering 10 seconds)                        | 260°C          |  |  |

| ESD(Including CDM <sup>(NOTE 3)</sup> HBM                      | (NOTE 4)       |  |  |

| CDM                                                            | ±1.5kV         |  |  |

| НВМ                                                            | ±2kV           |  |  |

| Latch-Up                                                       |                |  |  |

| Test condition: JESD78F                                        | +IT: 200mA     |  |  |

| Test condition. JESD/6F                                        | -IT: -200mA    |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: Based on simulations conducted with the device mounted on a JEDEC 4-layer PCB.

NOTE3: Test method: ESDA/JEDEC JS-002-2022;

NOTE4: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2023;

## **Recommended Operating Conditions**

| Symbol | Parameter                            | Condition             | Min.  | Тур. | Max. | Unit |

|--------|--------------------------------------|-----------------------|-------|------|------|------|

| VIN    | Input voltage                        |                       | 2.2   |      | 5.5  | V    |

| VOUT   | Output voltage                       |                       | 2.025 |      | 5.2  | V    |

|        |                                      | Vout=3.5V, VIN ≥ 2.2V | 0.8   |      |      | Α    |

| IOUT   | Output current                       | Vout=3.5V, VIN ≥ 2.5V | 1     |      |      | Α    |

|        |                                      | Vout=3.5V, VIN ≥ 3.3V | 1.5   |      |      | Α    |

| L      | Inductor                             |                       | 0.22  | 0.47 | 1    | μΗ   |

| Cin    | Input capacitor                      |                       |       | 10   |      | μF   |

| Соит   | Output capacitor                     |                       |       | 22   |      | μF   |

| ТА     | Operating free-air temperature range |                       | -40   |      | 85   | °C   |

Note: All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any de-rating effect, like a DC bias.

## **Electrical Characteristics**

$V_{IN}=3.8V$ ,  $V_{OUT}=3.5V$ ,  $T_A=25$ °C,  $C_{OUT}=22\mu F$ ,  $L=0.47\mu H$ , for typical values (unless otherwise noted)

| P                            | PARAMETER                                             | TEST CONDITION                                            | MIN   | TYP  | MAX  | UNIT |

|------------------------------|-------------------------------------------------------|-----------------------------------------------------------|-------|------|------|------|

| Vin                          | Input Operating<br>Voltage                            |                                                           | 2.2   |      | 5.5  | V    |

| V <sub>UVLO</sub>            | UVLO Threshold<br>Voltage                             | V <sub>IN</sub> rising                                    |       | 1.92 | 2.05 | V    |

|                              | Hysteresis For UVLO                                   |                                                           |       | 80   | 200  | mV   |

| I <sub>Q_SW</sub>            | Quiescent Current                                     | V <sub>EN</sub> =3.8V,I <sub>OUT</sub> =0A                | •     | 2.8  | 5    | μA   |

| IQ_NON SW                    | Quiescent Current                                     | V <sub>EN</sub> =3.8V,V <sub>OUT</sub> =3.8V,no switching |       | 2.3  | 5    | μA   |

| I <sub>SD</sub>              | Shutdown Current                                      | V <sub>EN</sub> =0V                                       |       | 0.3  | 1    | μA   |

| Vouт                         | Output Voltage Range                                  | . (                                                       | 2.025 |      | 5.2  | V    |

|                              |                                                       | V <sub>IN</sub> =2.2 - 2.5V, V <sub>OUT</sub> =3.5V       | 0.8   |      |      | Α    |

| Iout_max                     | Maximum Continuous Output Current                     | V <sub>IN</sub> ≥2.5V, V <sub>OUT</sub> =3.5V             | 1     |      |      | Α    |

|                              | Sulput Sulfont                                        | V <sub>IN</sub> ≥3.3V, V <sub>OUT</sub> =3.5V             | 1.5   |      |      | Α    |

| Voutvsel_l                   | Default Output Voltage                                | V <sub>SEL</sub> = low                                    |       | 3.3  |      | V    |

| Voutvsel_h                   | Default Output Voltage                                | V <sub>SEL</sub> = high                                   |       | 3.5  |      | V    |

| Rdischg                      | Output Discharge<br>Resistor                          | V <sub>EN</sub> = 0V                                      |       | 200  |      | Ω    |

| Acc_Forced <sup>NO</sup> TE1 | Output Voltage<br>Accuracy                            | Forced PWM operation                                      | -1    |      | 1    | %    |

| Acc_auto <sup>NOT</sup>      | Output Voltage<br>Accuracy                            | Auto PFM operation                                        | -1    |      | 3    | %    |

| Інм_виск                     | MOSFET Peak Current Limit                             | Buck operation                                            |       | 3.7  |      | Α    |

| ILIM_BOOST                   | MOSFET Peak<br>Current Limit                          | Boost operation                                           |       | 3    |      | Α    |

| Fsw                          | Switching Frequency                                   | Boost or Buck operation                                   | 1     | 1.6  |      | MHz  |

| V                            | Positive-Going Under-<br>Voltage Threshold<br>Voltage |                                                           | 92    | 95   | 98.5 | %    |

| Vuvp                         | Negative-Going<br>Under-Voltage<br>Threshold Voltage  |                                                           | 82    | 85   | 88   | %    |

| t <sub>ss</sub>              | Soft Start Time                                       |                                                           |       |      | 1    | ms   |

| t <sub>EN</sub>              | Enable Delay Time                                     |                                                           |       | 130  |      | μs   |

|                              | Output Voltage                                        | 0x01, bit[1:0] = 00b                                      |       | 1    |      | V/ms |

| Dvs_sr                       | Dynamic Voltage                                       | 0x01, bit[1:0] = 01b                                      |       | 2.5  |      | V/ms |

|                              | Scaling Slew Rate                                     | 0x01, bit[1:0] = 10b                                      |       | 5    |      | V/ms |

|                         |                                                | 0x01, bit[1:0] = 11b                                       |      | 10  |      | V/ms |

|-------------------------|------------------------------------------------|------------------------------------------------------------|------|-----|------|------|

| R <sub>DS(on)</sub> _Q1 | Buck High-Side Switch<br>On Resistance(Q1)     |                                                            |      | 50  |      | mΩ   |

| R <sub>DS(on) _Q2</sub> | Buck Low-Side Switch<br>On Resistance(Q2)      |                                                            |      | 50  |      | mΩ   |

| R <sub>DS(on)</sub> _Q3 | Boost Low-Side Switch<br>On Resistance(Q3)     |                                                            |      | 40  |      | mΩ   |

| R <sub>DS(on)</sub> _Q4 | Boost High-Side<br>Switch On<br>Resistance(Q4) |                                                            |      | 60  | >    | mΩ   |

| Іін                     | High-Level Input<br>Current                    | $V_{SCL} = V_{SDA} = V_{SEL} = 3.3V$ , no pull-up resistor |      |     | 1    | μA   |

| I <sub>B</sub>          | Input Bias Current                             | V <sub>EN</sub> = 3.8V                                     |      | 5   | 1    | μΑ   |

| I <sub>HS_LK</sub>      | High-Side Switch<br>Leakage Current            | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 0V                 |      |     | 1    | μA   |

| V <sub>EN_H</sub>       | Enable Input High<br>Threshold                 | V <sub>IN</sub> = 2.2V to 5.5V                             | 1.2  |     |      | V    |

| V <sub>EN_L</sub>       | EN Falling Threshold                           | V <sub>IN</sub> = 2.2V to 5.5V                             |      |     | 0.4  | V    |

| VIH                     | (SCL, SDA, VSEL)<br>Input High Threshold       |                                                            | 0.84 |     |      | V    |

| VIL                     | (SCL, SDA, VSEL)<br>Input Low Threshold        |                                                            |      |     | 0.36 | V    |

| T                       | Over Temperature<br>Protection                 | -0                                                         |      | 145 |      | °C   |

| Тотр                    | Over Temperature<br>Hysteresis                 |                                                            |      | 20  |      | °C   |

Note1: The minimum and/or maximum limits are guaranteed via production testing (under a subset of conditions) and/or characterization. Full coverage across all specified conditions is not achieved through production testing alone.

## I<sup>2</sup>C Characteristics

|                                  | PARAMETER                                             | TEST CONDITION | MIN  | TYP  | MAX  | UNIT |

|----------------------------------|-------------------------------------------------------|----------------|------|------|------|------|

| Vi <sup>2</sup> col              | Logic Output Threshold<br>Voltage (SCL, SDA,<br>VSEL) |                |      |      | 0.4  | V    |

| VI <sup>2</sup> Cint             | I <sup>2</sup> C Work Voltage                         |                |      | 1.8  |      | μΑ   |

| lın_ı²c                          | Input Current Each IO Pin                             |                | -10  |      | 10   | μΑ   |

| t <sub>DS_l</sub> 2 <sub>C</sub> | Data Set-Up Time                                      |                | 70   | 970) | 7    | ns   |

| fclk                             | SCL Clock Frequency                                   |                | 100  | 400  | 1000 | kHz  |

| t <sub>BUF</sub>                 | Bus Free Time between<br>Stop and Start<br>Condition  |                | 0.5  |      |      | μs   |

| thd;sta                          | Hold Time (Repeated) START Condition                  | X              | 0.26 |      |      | μs   |

| tsu;sta                          | Set-Up Time for a<br>Repeated START<br>Condition      |                | 0.26 |      |      | μs   |

| t <sub>HD;DAT</sub>              | Data Hold Time                                        |                | 0.1  |      |      | ns   |

| t <sub>SU;STO</sub>              | Set-Up Time for STOP<br>Condition                     | <b>20</b>      | 0.26 |      |      | μs   |

| t <sub>VD;ACK</sub>              | Data Valid<br>Acknowledge Time                        |                |      |      | 0.45 | μs   |

| t <sub>SU;DAT</sub>              | SDA Set-Up Time                                       |                | 50   |      |      | ns   |

| t <sub>LOW</sub>                 | Low Period of the SCL<br>Clock                        |                | 0.5  |      |      | μs   |

| thigh                            | High Period of the SCL<br>Clock                       |                | 0.26 |      |      | μs   |

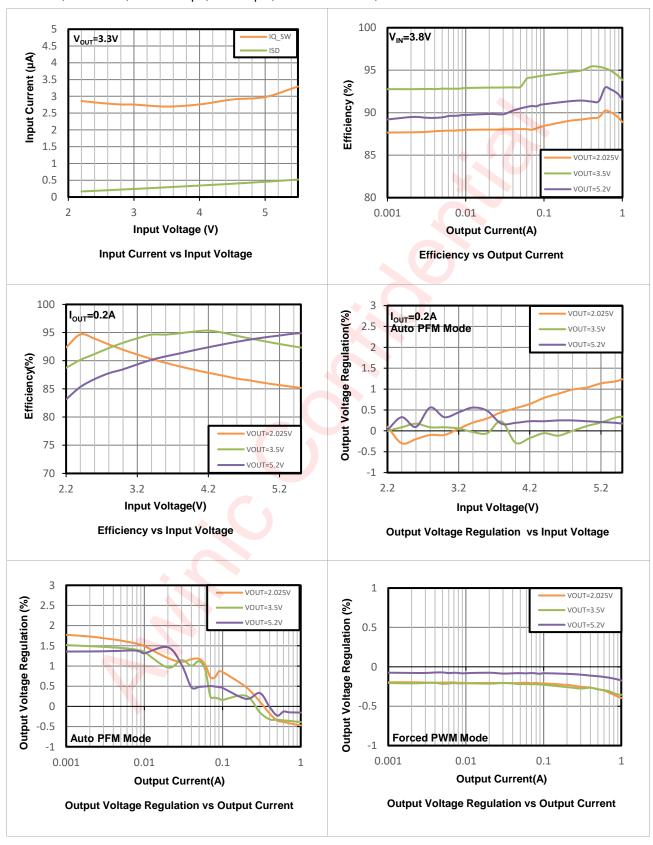

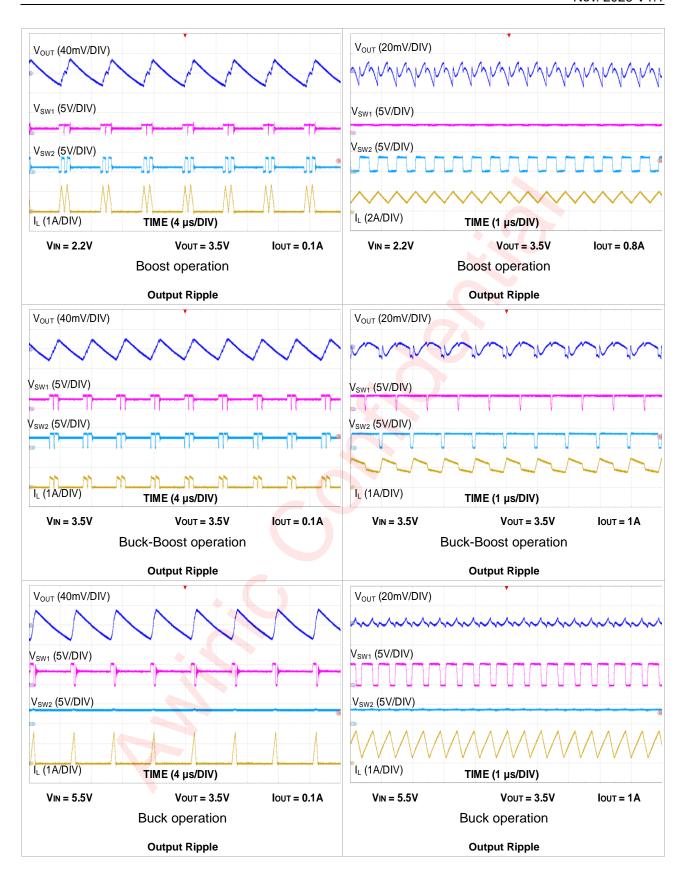

## **Typical Characteristics**

$T_A$ =25°C ,  $V_{IN}$ =3.8V ,  $C_{OUT}$  =22  $\mu F$ , L=0.47 $\mu H$ , Auto PFM mode, unless otherwise noted .

## **Detailed Functional Description**

#### **Control Scheme**

AWP37701Z uses emulated current ripple constant on-time control scheme where an outer voltage control loop generates the demand signal for an inner emulated current control loop. During the off-time, the control loop monitors the emulated current ripple signal with demand signal, and when the emulated current signal equals the demand signal from the error amplifier, the off-time stops and the next on-time of the switching cycle starts. The on-time is a function of VIN and VOUT. In this way, a pseudo-fixed switching frequency can be achieved for different input and output voltages.

This control method results in excellent dynamic response for the chip. For instance, when VIN=3.8V, VOUT=3.5V, and IOUT ranges from 0 to 0.3A, the chip maintains stable performance under repeated load draws. Specifically, after applying the load for 10 µs, The difference between the output voltage's persistence and ripple remains within 10 mV. This indicates the chip's ability to efficiently handle rapid changes in load current and maintain voltage stability, which is crucial for many electronic applications requiring consistent power supply performance.

#### **Operation Mode**

AWP37701Z automatically switches between buck, boost, and buck-boost operation as required by the VIN and VOUT operating conditions. The transition between different operating mode (buck, boost, or buck-boost) of the converter is automatic and seamless. AWP37701Z operates as a true buck converter when VIN > VOUT. AWP37701Z operates as a true boost converter when VIN < VOUT. When VIN and VOUT gets closer the device operates in buck-boost mode.

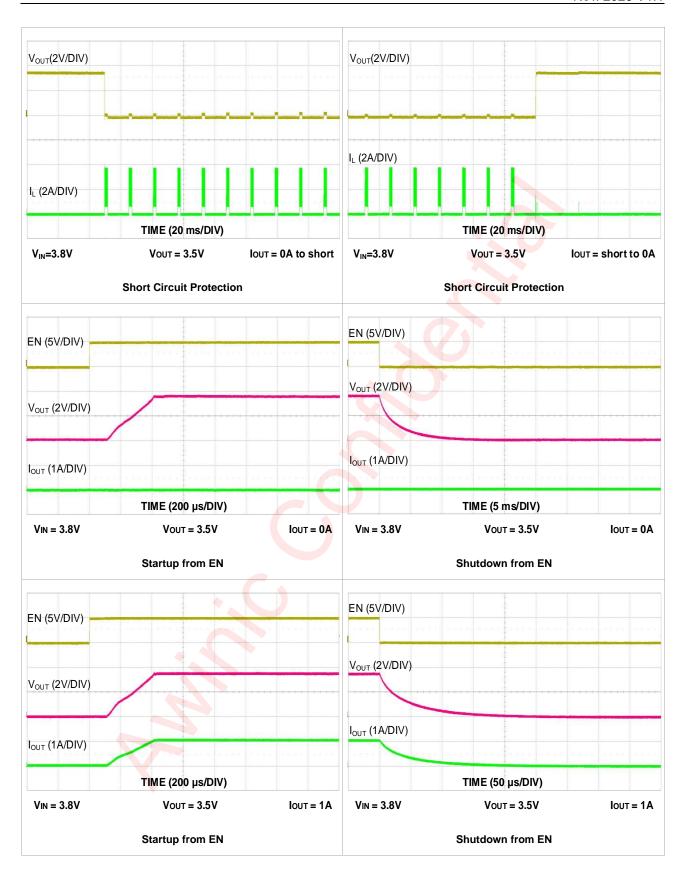

#### Soft-Start

An internal current source charges an internal capacitor to build the soft-start ramp voltage. During the soft-start period, PG is initially set to '0'. and when VOUT reaches 95% of its set voltage, the device sets PG to '1'. The rise time of the output voltage changes with the application circuit and the operating conditions. The Enable Delay Time is set to 0.13mS, the soft-start time is set to 0.25mS. The output voltage rise time increases if the load current is large or the output capacitance is large.

#### **VSEL**

VSEL = L output voltage default setting is 3.3V that can be programmed by Address 0x04[6:0] VOUT1.

VSEL = H output voltage default setting is 3.5V that can be programmed by Address 0x05[6:0] VOUT2.

VSEL = L the device address should be configured to 76h (1110110b).

VSEL = H the device address should be configured to 75h (1110101b).

The VSEL pin is compatible with 1.8V and 3.3V voltage levels.

#### **Auto PFM (Pulse Frequency Modulation) Mode**

In order to save power and improve efficiency at low loads, the Buck/Boost operate in PFM (Pulse Frequency Modulation) mode to save power. During PFM mode, the switching frequency is proportional to loading to reach output voltage regulation. When load increases and inductor current becomes continuous again, the Buck/Boost automatically goes back to PWM fixed frequency mode.

Additionally, AWP37701Z will enter Deep Sleep Mode to achieve extremely low quiescent current when there's no load. (see Deep Sleep Mode for more information).

#### **Deep Sleep Mode**

AWP37701Z is suitable for low quiescent current applications. When there's no load, AWP37701Z will automatic enter Deep Sleep Mode to achieve extremely low quiescent current. Once the load increases, it will go back to normal operation at once.

#### **FPWM (Forced Pulse Width Modulation) Mode**

The switching frequency is forced into PWM mode operation. In this mode, the inductor current is in CCM (Continuous Current Mode) and the voltage is regulated by PWM control.

To enable Forced-PWM operation, set the FPWM bit (Address 0X01[3]) to '1'.

#### **VOUT Program**

The AWP37701Z supports programmable VOUT from 2.025V to 5.2V with 25mV resolution. The output voltage can be set by register bit and the output voltage is given by the following equation:

VOUT = 2.025V + VOUTreg x 25mV

For example:

If VOUTreg = 110011 binary (51 decimal), then VOUT = 2.025V + 51 x 25mV = 2.025V + 1.275V = 3.3V.

AWP37701Z also has external VSEL pin to select VOUT1 (Address 0X04[6:0]) or VOUT2 (Address 0X05[6:0]). Pulling VSEL to high is for VOUT2 and pulling VSEL to low is for VOUT1. Upon POR, VOUT1 and VOUT2 are reset to their default voltages.

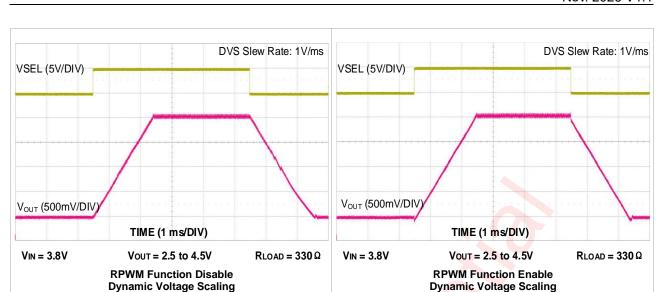

#### **Dynamically Voltage Scaling Control**

The AWP37701Z supports programmable slew-rate control feature when both increasing and decreasing the output voltage, which is known as Dynamically Voltage Scaling (DVS). The ramp slew-rate can be set to 1V/mS, 2.5V/mS, 5V/mS or 10V/mS through bit1 and bit0 of control register. Moreover, the operation mode during DVS region can be adjusted through control register RPWM bit. When Ramp-PWM function is activated, the device will change to Forced PWM mode operation during DVS region and change back to auto PFM mode after reaching target output(see the Ramp-PWM Function for more information).

#### Ramp-PWM Function

If Ramp-PWM function is enabled, the device operates in FPWM(Forced Pulse Width Modulation) when it ramps from one output voltage to another during dynamic voltage scaling. This function is useful when you want to make sure that dynamic voltage scaling ramps the output voltage up and down in a controlled way. If the device operates in Auto PFM Mode and Ramp-PWM is enabled, the device allows both sink and source current from device output. If the device operates in Auto PFM Mode and Ramp-PWM is disabled, the devices cannot always control the ramp from a higher output voltage to a lower output voltage, because in Auto PFM or PWM Mode the devices cannot sink current from device output.

To enable Ramp-PWM function, set the RPWM bit (Address 0X01[2]) to '1'.

To disable Ramp-PWM function, clear the RPWM bit (Address 0X01[2]) to '0'.

#### **Enable**

The AWP37701Z provides an EN pin, as an external chip enable control, to enable or disable the device. If VEN is held below a logic-low threshold voltage, switching is inhibited even if the VIN voltage is above VIN undervoltage lockout threshold. During shutdown mode, the converter is disabled and all registers will reset to default value. During shutdown mode, the supply current can be reduced to I<sub>SD</sub>. A discharge event happens when the EN pin pulls from high to low (see the Discharge for more information). The EN pin is compatible with 1.8V and 3.3V voltage levels.

#### **Discharge**

The discharge event happens when the EN pin pulls from high to low. A typical  $200\Omega$  resistor is connected from output to ground when discharge starts. The discharge event lasts for 20m seconds.

#### **Over-Current Protection**

The device features a cycle-by-cycle current limit circuit, which limits the peak inductor current in the event of an overload. The exact value of the maximum inductor current during an overload is determined by the inductor current rising rate (e.g., operating conditions) and the converter's response delay time (e.g., switching mode).

#### **Input UVLO Protection**

In addition to the EN pin, the AWP37701Z also provides enable control through the VIN pin. If VEN rises above  $V_{ENH}$  first, switching will still be inhibited until the VIN voltage rises above  $V_{UVLO}$ . It is to ensure that the internal regulator is ready so that operation with not-fully-enhanced internal MOSFET switches can be prevented. After the device is powered up, if the VIN voltage goes below the UVLO falling threshold voltage ( $V_{UVLO}$  -  $\Delta V_{UVLO}$ ), this switching will be inhibited; if VIN voltage rises above the UVLO rising threshold ( $V_{UVLO}$ ), the device will resume switching. During shutdown mode, the converter is disabled and all registers will reset to default value.

#### **Over-Temperature Protection**

When the junction temperature exceeds the OTP threshold value, the IC will shut down the switching operation. Once the junction temperature cools down and is lower than the OTP lower threshold, the converter will automatically resume switching. When the device detects an over-temperature condition, it asserts the TSD\_STATUS bit (Address 0X02[4]) and the TSD\_FLAG bit (Address 0X02[1]) to '1'. The TSD\_STATUS bit (Address 0X02[4]) is automatically set to '0' when the junction temperature of the device is below 130°C. Similarly, the device clears the TSD\_FLAG bit (Address 0X02[1]) to '0' upon reading the Status register.

#### **Over-Voltage Protection**

The AWP37701Z integrates an Output Ove-Voltage Protection (OVP) circuit to protect the system and downstream components from potential damage caused by excessive voltage levels. When the output voltage exceeds 5.7V, the OVP circuit is triggered, disabling the power switch to prevent damage. Once the output voltage drops below 5.4V, the OVP condition is cleared, and the power switch resumes normal operation. This ensures reliable protection of the system during overvoltage events.

#### **Under-Voltage Protection**

The AWP37701Z provides Hiccup Mode for Under-Voltage Protection (UVP). When the VOUT voltage drops below 85% of Target VOUT, the UVP function will be triggered to shut down switching operation, During this condition, the Power Good (PG) bit (Address 0X02[0]) is set to '0'. If the UVP condition remains for a period, the AWP37701Z will retry to build up output voltage automatically. When the UVP condition is removed, the converter will soft-start to target voltage and resume normal operation.

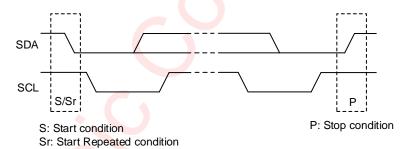

#### Interface

The AWP37701Z supports the I<sup>2</sup>C-Bus specification up to 1 MHz and operates in slave mode, supporting 7-bit addressing.

Register contents remain intact as long as VIN supply voltage remains above VIN undervoltage lockout threshold and EN voltage above logic-high threshold voltage. To make sure that the I<sup>2</sup>C transfer function is

correctly reset, it is recommended that the I<sup>2</sup>C master initiates a STOP condition on the I<sup>2</sup>C bus after the initial power up of SDA and SCL pullup voltages.

#### I<sup>2</sup>C INTERFACE

The AWP37701Z supports the I<sup>2</sup>C protocol. The maximum frequency supported by the I<sup>2</sup>C is 1MHz. The pull-up resistor for the SDA and SCL can be selected from  $1k\Omega$  to  $10k\Omega$ . Usually,  $4.7k\Omega$  is recommended for 400 kHz I<sup>2</sup>C,  $1k\Omega$  is recommended for 1MHz I<sup>2</sup>C. The voltage from 1.2V to 3.3V is allowed for the I<sup>2</sup>C interface. Additionally, the I<sup>2</sup>C device supports continuous reading and writing operations.

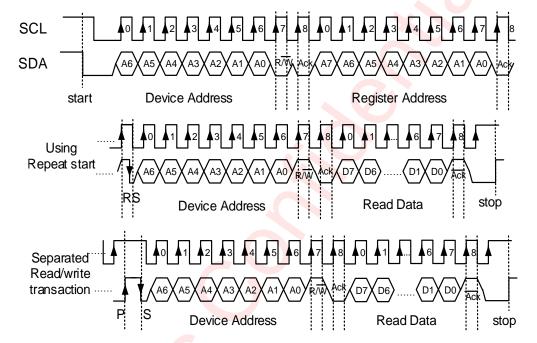

#### **DEVICE ADDRESS**

The I<sup>2</sup>C device address is 7-bit (A7~A1), when the VSEL pin is connected to logic low, the device address should be configured to 76h (1110110b); The VSEL pin is connected to logic high, the device address should be configured to 75h (1110101b). Followed by the R/W bit A0 (Read=1/Write=0). Set A0 to "0" for writing and "1" for reading.

For example, The VSEL pin is connected to logic low.

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0  |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 1  | 0  | 1  | 1  | 0  | R/W |

#### I<sup>2</sup>C START/STOP

I<sup>2</sup>C Start: SDA changes from high level to low level when SCL is high level.

I<sup>2</sup>C Stop: SDA changes from low level to high level when SCL is high level.

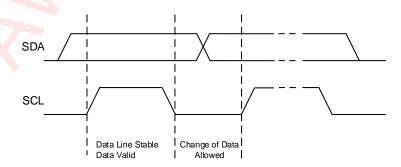

#### **DATA VALIDATION**

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

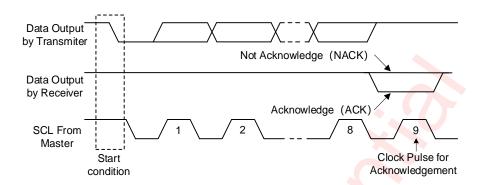

#### **ACK (ACKNOWLEDGEMENT)**

ACK means the successful transition of I<sup>2</sup>C bus data. After master sends an 8-bit data, SDA must be released;

SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8-bit data, releases the SDA and waits for ACK from master. If ACK is sent and I<sup>2</sup>C STOP is not sent by master, slave device sends the next data. If the master sends NACK, slave device stops to send data and waits for I<sup>2</sup>C stop.

#### **WRITE CYCLE**

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a start condition, a number of byte transfers (set by the software) and a stop condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- Master device generates Start condition. The "Start" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit R/W = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit).

- e) Slave sends acknowledge signal.

- f) Master sends data byte to be written to the addressed register.

- g) Slave sends acknowledge signal.

- h) If master will send further data bytes the control register address will be incremented by one after acknowledge signal (repeat step f and g).

- i) Master generates Stop condition to indicate write cycle end.

#### **READ CYCLE**

In a read cycle, the following steps should be followed:

- a) Master device generates Start condition.

- b) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit).

- e) Slave sends acknowledge signal.

- f) Master generates Stop condition followed with Start condition or Repeat Start condition.

- g) Master device sends slave address (7-bit) and the data direction bit (R/W = 1).

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends data byte from addressed register.

- j) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register.

- k) If the master device generates Stop condition, the read cycle ends.

## **Register Description**

| Addr | Name                | Туре | Bit7         | Bit6                  | Bit5           | Bit4           | Bit3         | Bit2         | Bit1         | Bit0 | Init |

|------|---------------------|------|--------------|-----------------------|----------------|----------------|--------------|--------------|--------------|------|------|

| 0x01 | CONTROL             | R/W  | RESE         | RVED                  | ENABL<br>E     | RESER<br>VED   | FPWM         | RPWM         | SLEW         |      | 0x20 |

| 0x02 | STATUS              | R    | RESER<br>VED | SCP_ST<br>ATUS        | OCP_S<br>TATUS | TSD_ST<br>ATUS | SCP_FL<br>AG | OCP_F<br>LAG | TSD_FL<br>AG | PG   | 0x00 |

| 0x03 | DEVICE_IDEN<br>TITY | R    |              | DEVICE Manufacture ID |                |                |              |              | 0x40         |      |      |

| 0x04 | VOUT1               | R/W  | RESER<br>VED | VOUT1                 |                |                | 0x33         |              |              |      |      |

| 0x05 | VOUT2               | R/W  | RESER<br>VED |                       |                |                | VOUT2        |              |              |      | 0x3B |

## **Register Detailed Description**

#### 0x01: CONTROL

| Bit | Symbol   | Туре | Description                                                                                                                                     | Default |

|-----|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:6 | Reserved | R    | Reserved                                                                                                                                        | 00      |

| 5   | ENABLE   | R/W  | Control Operation of the Converter  0 = Converter operation disabled  1 = Converter operation enabled (default)                                 | 1       |

| 4   | Reserved | R/W  | Reserved                                                                                                                                        | 0       |

| 3   | FPWM     | R/W  | Set Forced PWM Operation 0 = Disable (default) 1 = Enable                                                                                       | 0       |

| 2   | RPWM     | R/W  | Set Ramp PWM Operation  0 = Disable (default)  1 = Enable                                                                                       | 0       |

| 1:0 | SLEW     | R/W  | Set the Slew Rate.  Set the slew rate of the output voltage change to a new value.  00 = 1V/ms (default)  01 = 2.5V/ms  10 = 5V/ms  11 = 10V/ms | 00      |

#### 0x02: STATUS

| Bit | Symbol     | Туре | Description                                                                                                           | Default |

|-----|------------|------|-----------------------------------------------------------------------------------------------------------------------|---------|

| 7   | Reserved   | R    | Reserved                                                                                                              | 0       |

| 6   | SCP_STATUS | R    | The status of the short circuit Function  0 = Normal operation (default)  1 = An short circuit event is occurring     | 0       |

| 5   | OCP_STATUS | R    | The status of the Over-Current Function  0 = Normal operation (default)  1 = An over-current event is occurring       | 0       |

| 4   | TSD_STATUS | R    | The status of the Over-Temperature Function 0 = Normal operation (default) 1 = An over-temperature event is occurring | 0       |

| 3   | SCP_FLAG   | R/C  | The status of the short circuit Function It is cleared only if this register is read                                  | 0       |

| T        | I                      | ( / / f 10                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------|------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          |                        | U = Normal operation (default)                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | 1 = An short circuit event was detected           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | The flag of the Over-Current Function             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| OCD FLAC | R/C                    | It is cleared only if this register is read       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| OCP_FLAG |                        | 0 = Normal operation (default)                    | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|          |                        | 1 = An over-current event was detected            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | The flag of the Over-Temperature Function         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| TOD FLAG | D/0                    | It is cleared only if this register is read       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| TSD_FLAG | R/C                    | 0 = Normal operation (default)                    | U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|          |                        | 1 = An over-temperature event was detected        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | Output Power-Good                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | if the power-not-good condition no longer exists. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | 0 = A power-not-good event was detected. The      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| PG       | R                      | output voltage is below the PG voltage threshold  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| . 0      |                        | with a 1ms deglitch time (default)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | 1 = Power-good. The output voltage exceeds the    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          |                        | PG voltage threshold with a 1ms deglitch time     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|          | OCP_FLAG  TSD_FLAG  PG | TSD_FLAG R/C                                      | The flag of the Over-Current Function It is cleared only if this register is read 0 = Normal operation (default) 1 = An over-current event was detected  The flag of the Over-Temperature Function It is cleared only if this register is read 0 = Normal operation (default) 1 = An over-temperature event was detected  Output Power-Good if the power-not-good condition no longer exists. 0 = A power-not-good event was detected. The output voltage is below the PG voltage threshold with a 1ms deglitch time (default) 1 = Power-good. The output voltage exceeds the |  |

## 0x03: DEVICE\_IDENTITY

| Bit | Symbol            | Туре | Description    | Default |

|-----|-------------------|------|----------------|---------|

| 7:4 | Device            | R    | Device ID      | 0100    |

| 3:0 | Manufacture<br>ID | R    | Device VERSION | 0000    |

#### 0x04: VOUT1

| Bit | Symbol   | Туре | Description                                                                                                                           | Default |

|-----|----------|------|---------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | Reserved | R    | Reserved                                                                                                                              | 0       |

| 6:0 | VOUT1    | R/W  | VOUT1 register determines the device output voltage if the VSEL pin is logic low. VOUT = 2.025 + (VOUT1[6:0] × 0.025)V (default 3.3V) | 0110011 |

#### 0x05: VOUT2

| Bit | Symbol     | Туре | Description                                                                                                                            | Default |

|-----|------------|------|----------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7   | Reserved R |      | Reserved                                                                                                                               | 0       |

| 6:0 | VOUT2 R/W  |      | VOUT2 register determines the device output voltage if the VSEL pin is logic high. VOUT = 2.025 + (VOUT1[6:0] × 0.025)V (default 3.5V) | 0111011 |

## **Application Information**

#### **Typical Application**

Figure 4 AWP37701Z Typical Application Circuit

NOTE: When the output current is ≤1A, a 22µF COUT is recommended. When the output current is >1A, 2 × 22µF COUT capacitors are recommended. The recommended maximum output current should not exceed 1.5A.

#### **Inductor Selection**

The AWP37701Z recommended nominal inductance value is  $0.47\mu H$  to achieve advantage performance. For high efficiencies, use an inductor with a low DC resistance (DCR) and low core losses.

The saturation current of the inductor must be greater than the maximum inductor current in your application. To include sufficient margin for worst-case and transient operating conditions, The AWP37701Z recommends you use an inductor with saturation current that is at least 20% higher than the maximum inductor current in your application. The maximum current in the inductor occurs when the device operates in boost mode and the following is true:

The input voltage is at its minimum value.

The output voltage is at its maximum value.

The output current is at its maximum value.

To calculate the maximum inductor current, first calculate the maximum duty cycle during boost operation (which is when the maximum inductor current occurs).

$$Duty_{Max} = \frac{(V_{OUTMax} - V_{INMin})}{V_{OUTMax}}$$

Next, calculate the maximum inductor current.

$$I_{LMAX} = \frac{I_{OUTMax}}{\eta \bullet (1 - Duty_{Max})} \bullet \frac{Duty_{Max} \bullet V_{INMin}}{2 \bullet f_{SW} \bullet L}$$

To include enough margin for transient conditions, The AWP37701Z recommends you use an inductor with a saturation current rating at least 20% higher than the calculated maximum current.

#### Input capacitor Selection

Steady state and transient response operation performance also depend on input voltage stability or not. The AWP37701Z at least a  $10\mu F$  input capacitor is recommended to prevent input voltage instability with application operation. And that suggest placed as close as possible to the VIN and GND pins of the IC is recommended. If the input supply is more than a few centimeters from the device, we recommend you add some bulk capacitance to the ceramic bypass capacitors. A  $100\mu F$  electrolytic capacitor is a typical selection for the bulk capacitance.

#### **Output capacitor Selection**

The ripple voltage is an important index for choosing output capacitor. This portion consists of two parts. One is the product of ripple current with the ESR of the output capacitor, while the other part is formed by the charging and discharging process of the output capacitor. Output capacitor is selected according to output ripple which is calculated as below equation.

$$\begin{split} \Delta V_{OUT} &= \Delta V_{ESR} + \Delta V_{OUTCAP} \\ \Delta V_{ESR} &= I_{CRMS} \bullet R_{CESR} \\ \Delta V_{OUTCAP} &= \frac{I_{OUT} \bullet Duty}{f_{SW} \bullet C_{OUTMIN}} \end{split}$$

User can use equation choose capacitor to meeting systems ripple specification. When the IOUT is  $\leq 1A$ , at least  $22\mu\text{F}/16\text{V}/\text{X}5\text{R}$  capacitors is recommended to matching application with VOUT ripple request and stability performance. When the IOUT is >1A, at least  $2*22\mu\text{F}/16\text{V}/\text{X}5\text{R}$  capacitors are recommended to matching application with VOUT ripple request and stability performance.

## **PCB Layout Consideration**

The AWP37701Z is a synchronous buck-boost converter, to obtain the optimal performance, PCB layout should be considered carefully. Here are some guidelines:

- 1. C<sub>IN</sub>, C<sub>OUT</sub> should be placed as close to chip as possible.

- 2. Wide and short traces should be used for main current path and the power ground paths.

- 3. Switching node (SW1 and SW2) are with high frequency voltage swing and should be kept at small area. Keep analog components away from the SW1 and SW2 node to prevent stray capacitive noise pickup.

Top layer

Bottom layer

VIA

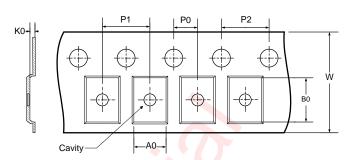

## **Tape And Reel Information**

# **REEL DIMENSIONS** 0 D1 D0

#### TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

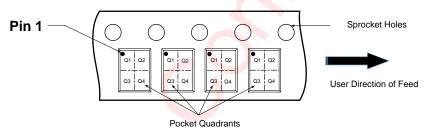

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### DIMENSIONS AND PIN1 ORIENTATION

|   | D1     | D0   | A0   | B0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant |  |

|---|--------|------|------|------|------|------|------|------|------|---------------|--|

| l | (mm)   | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) |               |  |

|   | 180.00 | 8.60 | 1.50 | 1.46 | 0.68 | 2.00 | 4.00 | 4.00 | 8.00 | Q1            |  |

All dimensions are nominal

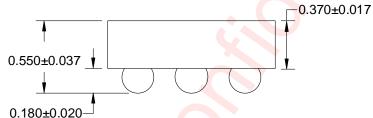

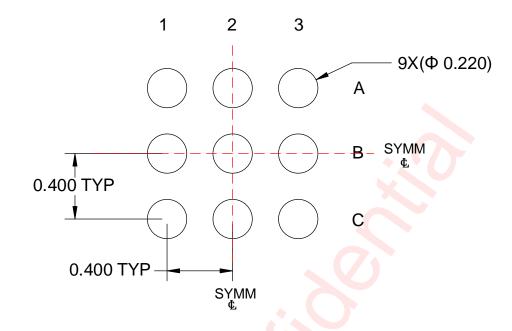

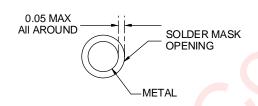

## **Package Description**

#### **Side View**

**Bottom View**

Unit: mm

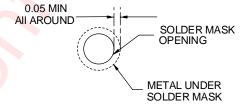

NON-SOLDER MASK DEFINED

**SOLDER MASK DEFINED**

Unit: mm

## **Revision History**

| Version | Date      | Change Record                                                                                          |

|---------|-----------|--------------------------------------------------------------------------------------------------------|

| V1.0    | Aug. 2025 | Officially released                                                                                    |

| V1.1    | Nov. 2025 | Update the description of the Vout ripple operation mode in the Typical Characteristics section. (P10) |

#### **Disclaimer**

All trademarks are the property of their respective owners. Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.